# **Time in wireless embedded systems**Schmid, Thomas *ProQuest Dissertations and Theses*; 2010; ProQuest Dissertations & Theses (PQDT) pg. n/a

University of California Los Angeles

# **Time in Wireless Embedded Systems**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

**Thomas Schmid**

2009

UMI Number: 3424179

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI 3424179

Copyright 2010 by ProQuest LLC.

All rights reserved. This edition of the work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

© Copyright by Thomas Schmid 2009 The dissertation of Thomas Schmid is approved.

Deborah Estrin

William J. Kaiser

Mani B. Srivastava, Committee Chair

University of California, Los Angeles 2009

To my wife ...

to my mother and father ...

to my sister and brother ...

for their endless encouragement and patience.

# Table of Contents

| 1  | Intr                              | oductio | n                                                          | 1        |

|----|-----------------------------------|---------|------------------------------------------------------------|----------|

|    | 1.1                               | A Sho   | rt History of Keeping Time                                 | 1        |

|    | 1.2                               | Accura  | ate Time in Modern Embedded Systems                        | 3        |

|    |                                   | 1.2.1   | LC/RC Circuits                                             | 6        |

|    |                                   | 1.2.2   | Ring Oscillator                                            | 8        |

|    |                                   | 1.2.3   | Quartz Crystal                                             | 8        |

|    |                                   | 1.2.4   | MEMS Resonators                                            | 13       |

|    |                                   | 1.2.5   | Other Types of Resonators                                  | 13       |

|    | 1.3                               | Contri  | butions                                                    | 14       |

| 2  |                                   | •       | al Designs for Temperature Induced Frequency Error Compen- |          |

| sa | tion                              | · · · · |                                                            | 16       |

|    | 2.1                               | Introd  | uction                                                     | 16       |

|    |                                   | 2.1.1   | Related Work                                               | 17       |

|    |                                   | 2.1.2   | Novel Approach                                             | 19       |

|    |                                   |         | Novel Apploach                                             |          |

|    | 2.2                               | Introd  | ucing Differential Drift                                   | 21       |

|    | <ul><li>2.2</li><li>2.3</li></ul> |         |                                                            | 21<br>23 |

|    |                                   |         | ucing Differential Drift                                   |          |

|    |                                   | The C   | ucing Differential Drift                                   | 23       |

|    |                                   | The C   | ucing Differential Drift                                   | 23<br>24 |

|   |     | 2.3.5     | Model Fitting Effects                  | 32 |

|---|-----|-----------|----------------------------------------|----|

|   |     | 2.3.6     | Quantization Effects                   | 32 |

|   |     | 2.3.7     | Other Effects                          | 35 |

|   | 2.4 | Algori    | thm Evaluation                         | 36 |

|   |     | 2.4.1     | Environment Emulator                   | 37 |

|   |     | 2.4.2     | Testbed                                | 37 |

|   |     | 2.4.3     | Interrupt Latency Considerations       | 39 |

|   |     | 2.4.4     | Limitations                            | 39 |

|   |     | 2.4.5     | Calibration                            | 40 |

|   |     | 2.4.6     | Compensation                           | 40 |

|   |     | 2.4.7     | Experimental Results                   | 43 |

|   | 2.5 | XCXT      | Hardware Implementation                | 47 |

|   |     | 2.5.1     | XCXT Power Measurements                | 49 |

|   |     | 2.5.2     | Microprocessor Power Consumption       | 49 |

|   |     | 2.5.3     | Oscillator and Timer Power Consumption | 51 |

|   | 2.6 | Discus    | ssion                                  | 54 |

|   |     | 2.6.1     | Crystal Compensated Crystal Oscillator |    |

|   |     |           | (XCXO)                                 | 54 |

|   |     | 2.6.2     | Cost – Performance Comparison          | 54 |

|   |     | 2.6.3     | The Smart Timer Unit                   | 56 |

|   | 2.7 | Summ      | ary                                    | 59 |

| 3 | The | Effect of | of Temperature on Time Synchronization | 60 |

|   | 3.1                      | Introduction                                                         | 60                               |

|---|--------------------------|----------------------------------------------------------------------|----------------------------------|

|   |                          | 3.1.1 Contribution                                                   | 62                               |

|   | 3.2                      | Understanding Power Consumption in Duty-Cycled Devices               | 62                               |

|   |                          | 3.2.1 Clock Stability and Duty Cycling                               | 63                               |

|   | 3.3                      | Clock-Characteristic Impacts on Resynchronization Rate               | 69                               |

|   |                          | 3.3.1 Temperature Effects on Frequency Error                         | 70                               |

|   |                          | 3.3.2 Time Synchronization Error                                     | 70                               |

|   |                          | 3.3.3 A More Realistic Bound on the Time Synchronization Error .     | 75                               |

|   |                          | 3.3.4 Verification Through Simulation                                | 77                               |

|   | 3.4                      | Bringing it All Together: Synchronization, Duty-Cycling, and Power . | 78                               |

|   | 3.5                      | Summary                                                              | 80                               |

|   |                          |                                                                      |                                  |

| 4 | Tem                      | perature Compensated Time Synchronization                            | 82                               |

| 4 | <b>Tem</b> 4.1           | Introduction                                                         | <b>82</b>                        |

| 4 |                          | •                                                                    |                                  |

| 4 | 4.1                      | Introduction                                                         | 82                               |

| 4 | 4.1<br>4.2               | Introduction                                                         | 82<br>85                         |

| 4 | 4.1<br>4.2<br>4.3        | Introduction                                                         | 82<br>85<br>87                   |

| 4 | 4.1<br>4.2<br>4.3        | Introduction                                                         | 82<br>85<br>87<br>90             |

| 4 | 4.1<br>4.2<br>4.3        | Introduction                                                         | 82<br>85<br>87<br>90<br>91       |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Introduction                                                         | 82<br>85<br>87<br>90<br>91       |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Introduction                                                         | 82<br>85<br>87<br>90<br>91<br>91 |

|    | 5.1   | Introdu  | action                                                          | 99   |

|----|-------|----------|-----------------------------------------------------------------|------|

|    |       | 5.1.1    | Architectural Requirements                                      | 100  |

|    | 5.2   | The Co   | ost of Time Synchronization                                     | 102  |

|    |       | 5.2.1    | The Flooding Time Synchronization Protocol                      | 103  |

|    |       | 5.2.2    | Time Synchronization Power Model                                | 106  |

|    |       | 5.2.3    | Power – Frequency Stability Equilibrium                         | 108  |

|    |       | 5.2.4    | Concrete Example using the Epic Sensor Network Platform .       | 109  |

|    | 5.3   | Exploi   | ting Dual-Clock Hardware Designs for Increased Time Resolution  | n110 |

|    |       | 5.3.1    | Sub- $\mu$ Second Time Synchronization Using the Dual-Clock Ap- |      |

|    |       |          | proach                                                          | 112  |

|    | 5.4   | A Pow    | er-Aware Timer Module, the HLTimer                              | 114  |

|    | 5.5   | Summa    | ary                                                             | 118  |

| 6  | Disc  | ussion & | & Conclusion                                                    | 120  |

|    | 6.1   | Low-P    | ower, High-Accuracy Time in Embedded Systems                    | 120  |

|    | 6.2   | Lookin   | ng Ahead                                                        | 123  |

| Re | feren | ces      |                                                                 | 124  |

# LIST OF FIGURES

| 1.1 | Basic block diagram of a clock circuit and associated timer hardware.             | 3  |

|-----|-----------------------------------------------------------------------------------|----|

| 1.2 | Relative Frequency Drift vs Cost of commercially available clock                  |    |

|     | sources. Data gathered from different vendors in Fall 2007                        | 5  |

| 1.3 | Picture of a tuning fork 32kHz crystal commonly found in embedded                 |    |

|     | systems to keep wall time. They are small, and consume $< 15\mu W$                | 9  |

| 1.4 | Frequency Drift vs Temperature for two AT-cut crystals. The crystals              |    |

|     | are cut at an angle of $35^{\circ}20' + \theta$                                   | 11 |

| 2.1 | Frequency Drift vs Temperature for an uncompensated AT-cut quartz                 |    |

|     | crystal oscillator and temperature compensated crystal oscillator (TCXO).         | 18 |

| 2.2 | Differential Frequency Drift vs Temperature for multiple pairs of differ-         |    |

|     | ently AT-cut oscillators. Note that the steeper the slope, the better it is       |    |

|     | for our compensation algorithm                                                    | 20 |

| 2.3 | Frequency Drift versus Difference of Frequency Drift for several pairs            |    |

|     | of AT-cut oscillators. The larger the full span of $\delta f_{12}$ the better our |    |

|     | algorithm can compensate                                                          | 22 |

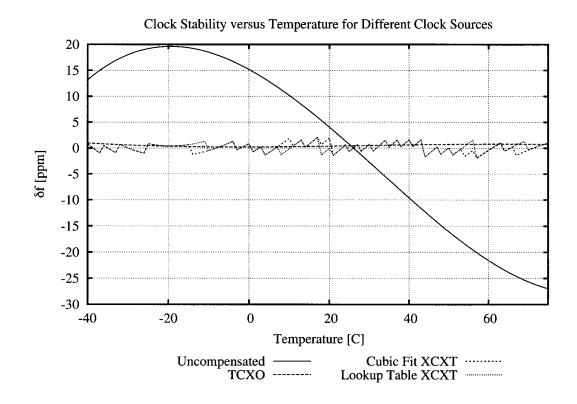

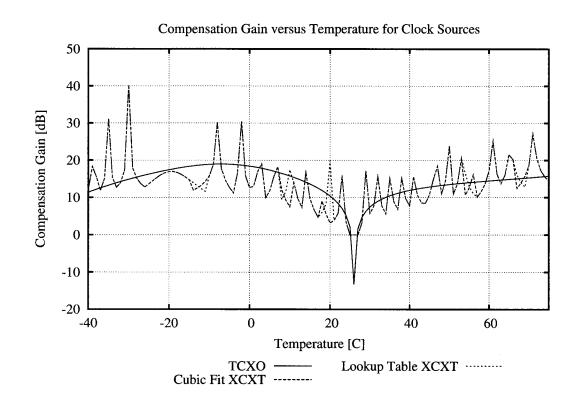

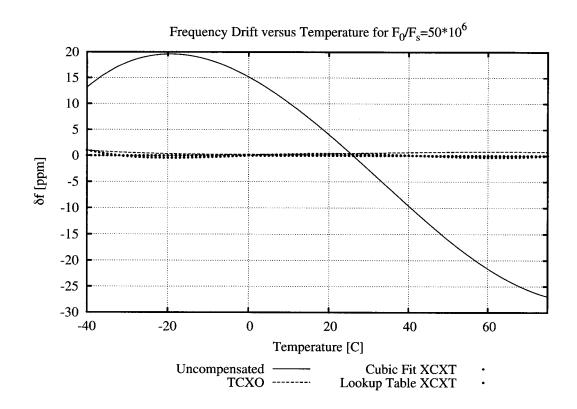

| 2.4 | Frequency Drift versus Temperature characteristics for Uncompensated,             |    |

|     | TCXO, Cubic Fit XCXT and Lookup Table XCXT                                        | 30 |

| 2.5 | Frequency Drift versus Temperature characteristics for Uncompensated,             |    |

|     | Temperature Compensated, Cubic Fit based Compensation and Lookup                  |    |

|     | Table based Compensation                                                          | 31 |

| 2.6 | Frequency Drift versus Temperature characteristics for Clock Source 2             |    |

|     | showing minimal effects due to quantization when $F_0/F_s = 50 \times 10^6$ .     | 33 |

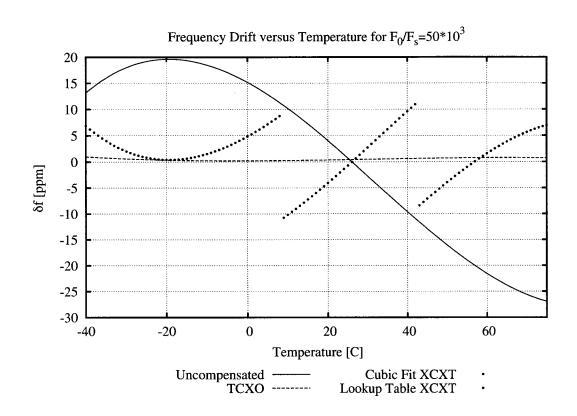

| 2.7  | Frequency Drift versus Temperature characteristics for Clock Source 2         |    |

|------|-------------------------------------------------------------------------------|----|

|      | showing detrimental effects of quantization when $F_0/F_s = 50 \times 10^3$ . | 34 |

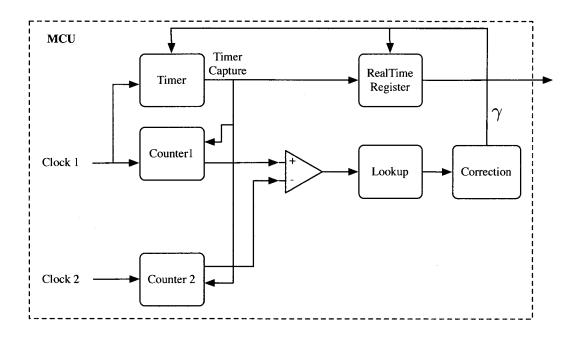

| 2.8  | Block diagram of the implementation of the XCXT                               | 3  |

| 2.9  | Experimental setup with the two Agilent waveform generators, the 2Hz          |    |

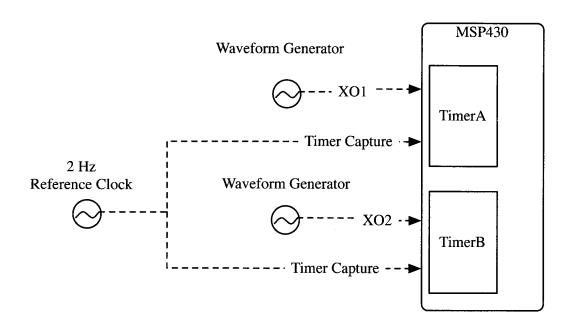

|      | reference clock, and the MSP430 microcontroller with its two timer units.     | 38 |

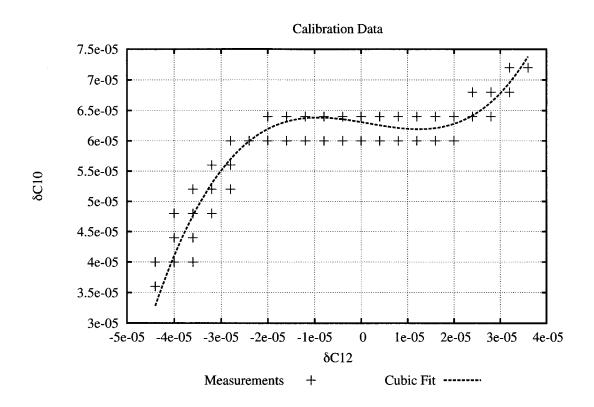

| 2.10 | Measured calibration and its cubic curve fit. Note the quantization           |    |

|      | effect which comes from measuring frequency difference with digital           |    |

|      | counters. The effect on error of this is discussed in Section 2.3.6           | 4  |

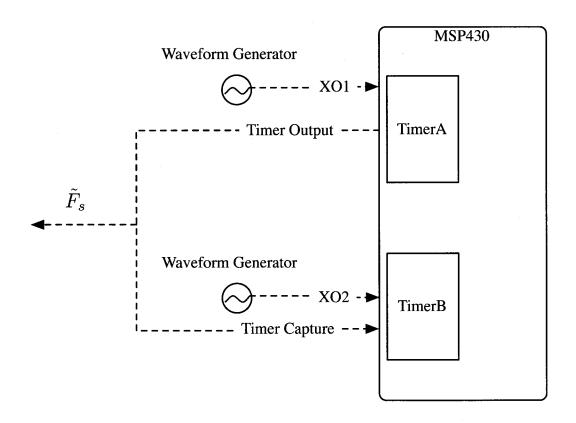

| 2.11 | Block diagram of our compensation experiment                                  | 42 |

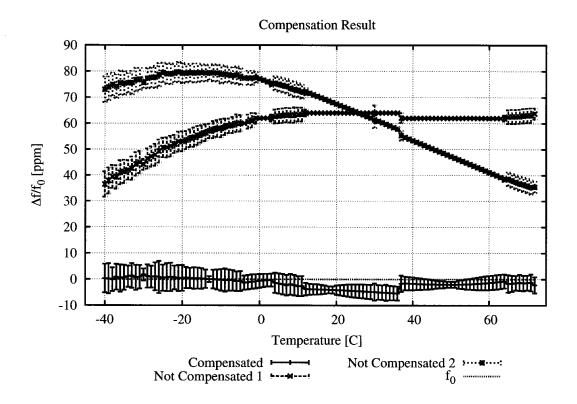

| 2.12 | Compensated clock drift over the full temperature range of -40° to 75°        |    |

|      | Celsius. We also show the drift of the two uncompensated crystals used        |    |

|      | in the compensation algorithm                                                 | 43 |

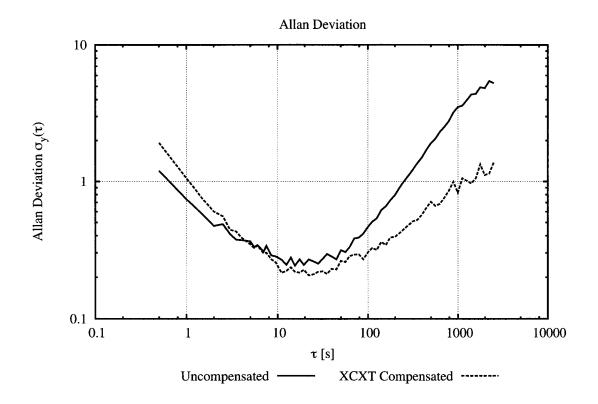

| 2.13 | Frequency stability expressed by the Allan Variance for the compen-           |    |

|      | sated and uncompensated clock. We can see that we trade short term            |    |

|      | vs. long term stability by employing our compensation algorithm               | 45 |

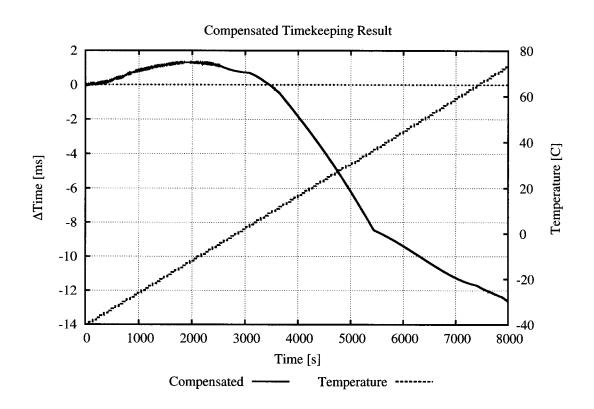

| 2.14 | Difference between global time and the estimated time at node 1 over          |    |

|      | 2.5 hour and a change in temperature from -40° to 75° Celsius. The            |    |

|      | different phases come from the inaccuracy introduced by the frequency         |    |

|      | generators, which not always set the output frequency to the desired          |    |

|      | frequency (see Figure 2.12)                                                   | 46 |

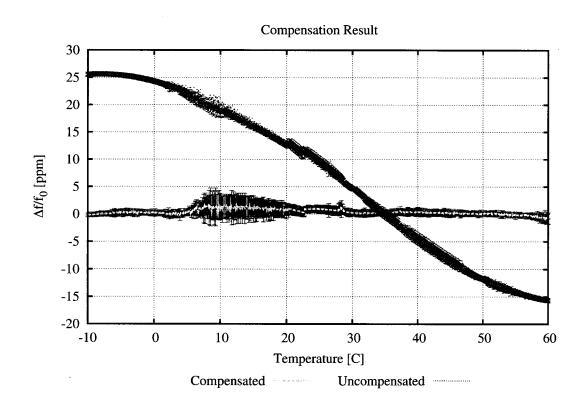

| 2.15 | Using the LUT from the calibration data, we can successfully com-             |    |

|      | pensate one of the crystals for its temperature drift. Over the full          |    |

|      | temperature range of -10°C to 60°C we measured a standard deviation           |    |

|      | of 0.31ppm                                                                    | 48 |

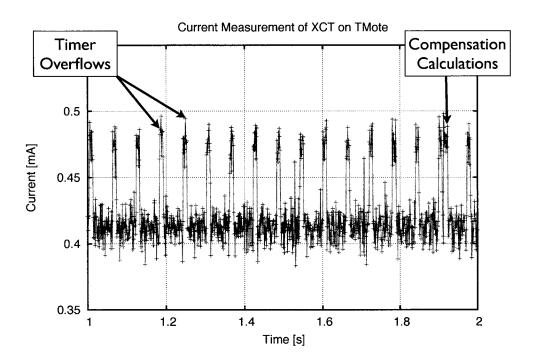

| This is a typical current consumption plot of the XCXT. The mea-             |                                                                                                                                                |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| surements were taken at 3V. The spikes represent instances when the          |                                                                                                                                                |

| microprocessor woke up because of a timer overflow which has to be           |                                                                                                                                                |

| treated                                                                      | 50                                                                                                                                             |

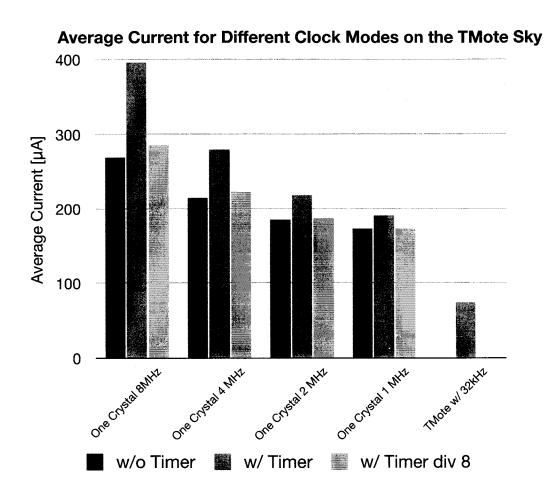

| These are the typical current consumptions of the clock and timer            |                                                                                                                                                |

| subsystem of the MSP430. The clock source was an 8MHz crystal,               |                                                                                                                                                |

| and the different clock speeds were achieved by dividing that signal         |                                                                                                                                                |

| using an internal clock divider. As comparison, we also measured the         |                                                                                                                                                |

| MSP430 power consumption when it uses a 32kHz crystal, one timer             |                                                                                                                                                |

| active, CPU turned off                                                       | 52                                                                                                                                             |

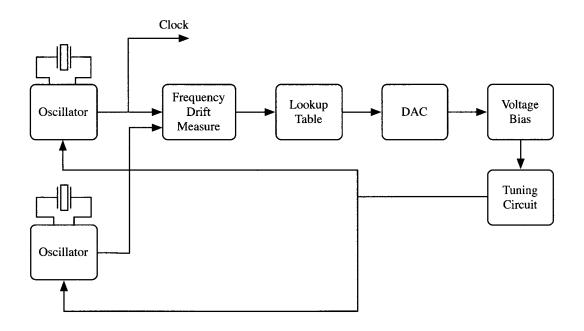

| Block diagram of an ideal hardware base Crystal Compensated Crystal          |                                                                                                                                                |

| Oscillator (XCXO)                                                            | 55                                                                                                                                             |

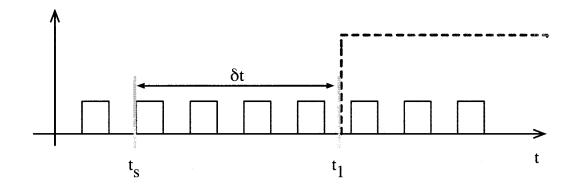

| This is the timeline of the smart timer unit. We can find the phase of       |                                                                                                                                                |

| the slower timer (red, dashed) since the time instance $t_s$ by counting the |                                                                                                                                                |

| number of ticks of the fast clock (blue, solid)                              | 57                                                                                                                                             |

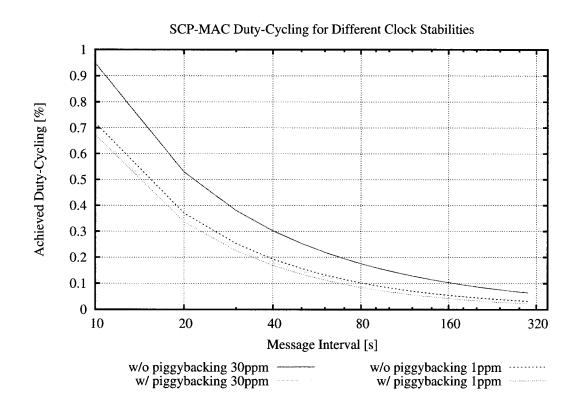

| Duty-Cycling performance of SCP-MAC using different clock source             |                                                                                                                                                |

| stabilities. Note that with a 1ppm clock source, the difference between      |                                                                                                                                                |

| piggybacking the sync messages on regular data messages or not virtu-        |                                                                                                                                                |

| ally disappears.                                                             | 65                                                                                                                                             |

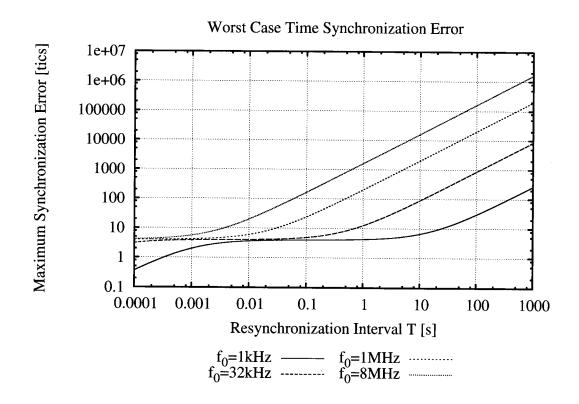

| Worst case time synchronization error for four different clock speeds.       |                                                                                                                                                |

| The two low frequency clocks are tuning fork crystals with a maximum         |                                                                                                                                                |

| frequency error of 120 ppm, and the high frequency clocks are AT-cut         |                                                                                                                                                |

| crystals with a maximum frequency error of ±50 ppm                           | 72                                                                                                                                             |

|                                                                              | surements were taken at 3V. The spikes represent instances when the microprocessor woke up because of a timer overflow which has to be treated |

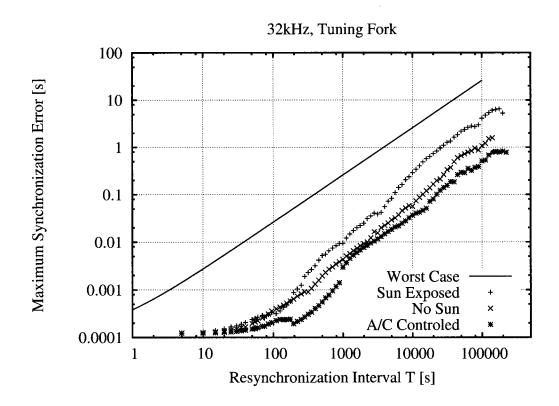

| 3.3 | This graph shows the effect of using the maximum drift change cal-            |    |

|-----|-------------------------------------------------------------------------------|----|

|     | culated from a temperature traces on the maximum synchronization              |    |

|     | error. In general, the smaller the temperature changes, the better the        |    |

|     | synchronization accuracy for longer resynchronization intervals               | 76 |

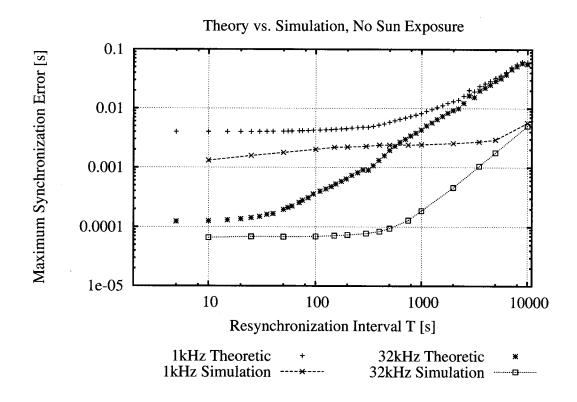

| 3.4 | This graph compares the theoretical upper bound to the 95% confidence         |    |

|     | interval found through simulating a time synchronization protocol             | 77 |

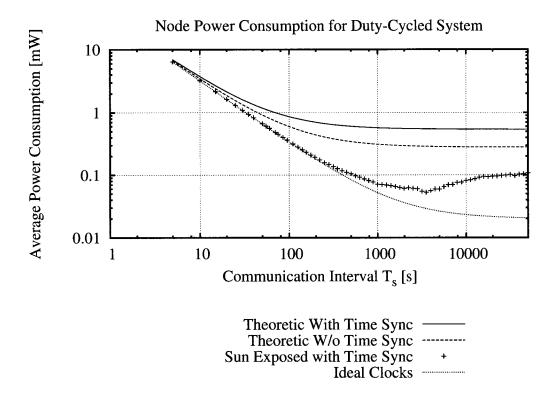

| 3.5 | This graphs shows the average power consumption for different syn-            |    |

|     | chronization techniques in a duty cycled system. With ideal clocks,           |    |

|     | no overhead is required, and thus a minimum power consumption is              |    |

|     | achieved. We only show the sun exposed data set because it is a worst         |    |

|     | case for the three temperature traces we collected                            | 79 |

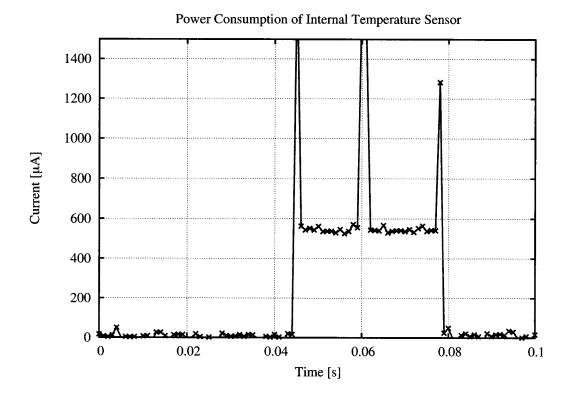

| 4.1 | Current profile of a TMote Sky while sampling the internal temperature        |    |

|     | sensor. It takes 35ms to wakeup the CPU, stabilize the internal voltage       |    |

|     | reference, take the sample, and shut down the CPU again. During that          |    |

|     | time, the node consumes a total of $66.5\mu J$ , or about 10% of what a radio |    |

|     | message consumes ( $\sim 600 \mu J$ )                                         | 85 |

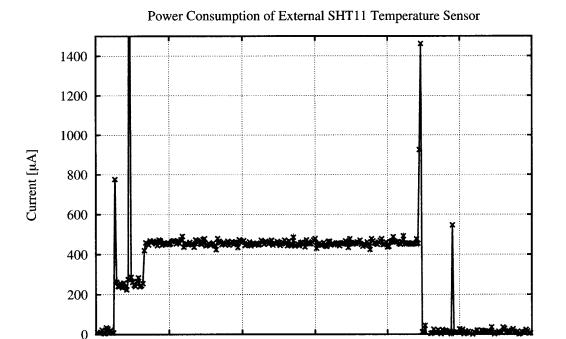

| 4.2 | This is the current consumption of a TMote Sky while sampling the             |    |

|     | external SHT11 temperature sensor. It takes a total of 220ms or about         |    |

|     | 287μJ                                                                         | 86 |

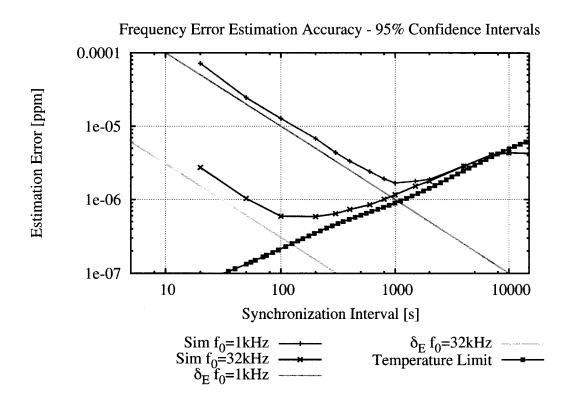

| 4.3 | The error in the frequency error estimation of a sensor node is ham-          |    |

|     | pered by two different phenomenas: (1) quantization due to the digital        |    |

|     | nature of a clock, and (2) temperature induced frequency drift. Simula-       |    |

|     | tion shows that there is an optimal resynchronization period at which         |    |

|     | estimation error is minimized.                                                | 88 |

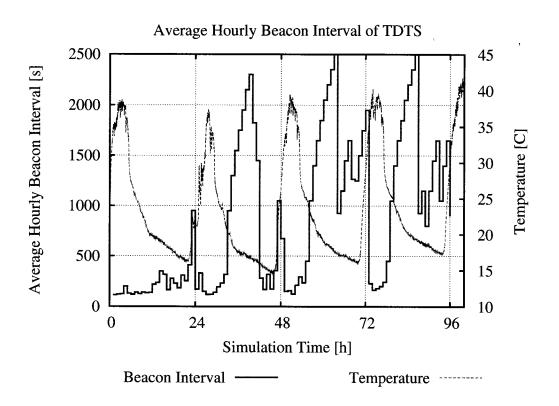

| 4.4 | This graph shows the hourly average resynchronization time. In the                  |     |

|-----|-------------------------------------------------------------------------------------|-----|

|     | first 24h, TCTS calibrates the local clock, and thus uses a very short              |     |

|     | synchronization period. Once calibrated, the resynchronization time                 |     |

|     | rapidly increase and thus saves power and communication overhead                    | 93  |

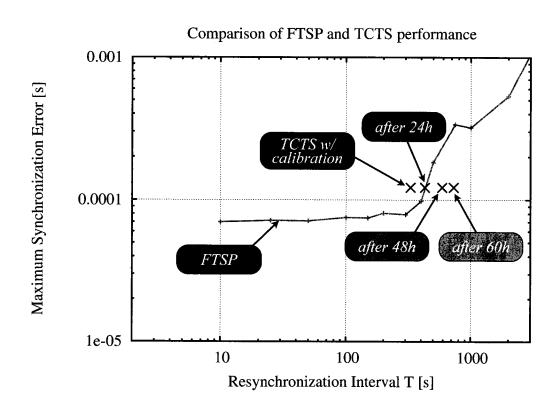

| 4.5 | If one ignores the one-time calibration overhead, TCTS quickly outper-              |     |

|     | forms FTSP in terms of accuracy with long resynchronization intervals.              |     |

|     | This is for a 32kHz tuning fork crystal                                             | 95  |

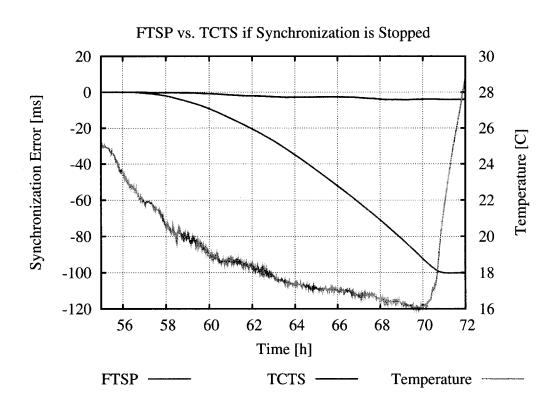

| 4.6 | Illustration of what happens if time synchronization is stopped. We                 |     |

|     | can clearly see how FTSP's performance worsens once the temperature                 |     |

|     | starts to change, whereas TCTS keeps the synchronization accuracy at                |     |

|     | a much higher level                                                                 | 96  |

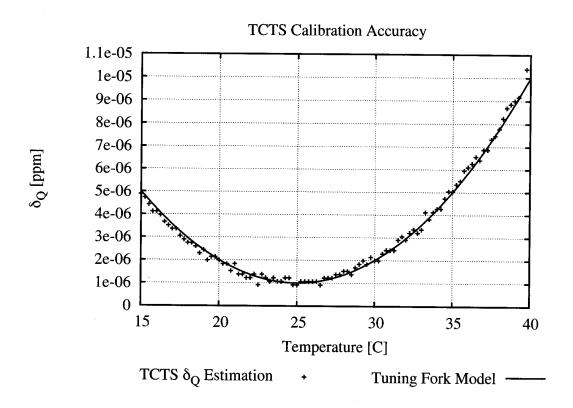

| 4.7 | TCTS estimates the frequency drift function $g(\kappa)$ for the current tem-        |     |

|     | perature, and stores it in a calibration table. In our simulation, $g(\kappa)$ is a |     |

|     | quadratic curve, as found in the tuning fork crystals. Even with only a             |     |

|     | 0.25C temperature resolution, the performance of TCTS is extremely                  |     |

|     | high                                                                                | 97  |

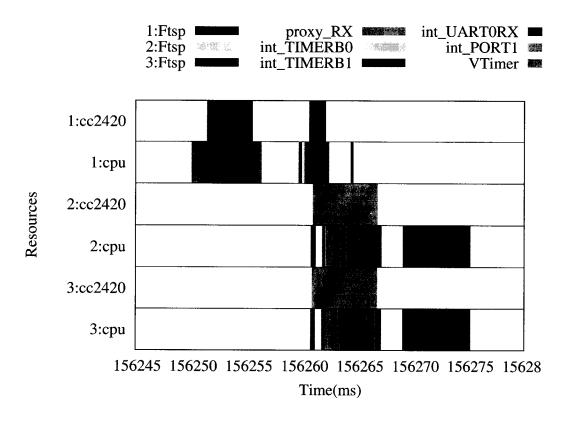

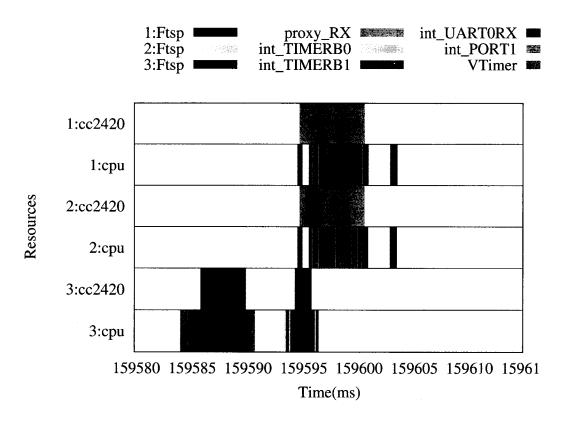

| 5.1 | Time synchronized Quanto Activity log of three nodes participating                  |     |

|     | in time synchronization. Node 1 sent out a timestamped broadcast                    |     |

|     | message. Node 2 and 3 receive the message and process it, since Node                |     |

|     | 1 is their synchronization root node                                                | 105 |

| 5.2 | Time synchronized Quanto Activity log of three nodes participating                  |     |

|     | in time synchronization. Node 3 sent out a timestamped broadcast                    |     |

|     | message. However, since 3 is not the synchronization parent of node 1               |     |

|     | or 2, they both just receive and then discard it                                    | 106 |

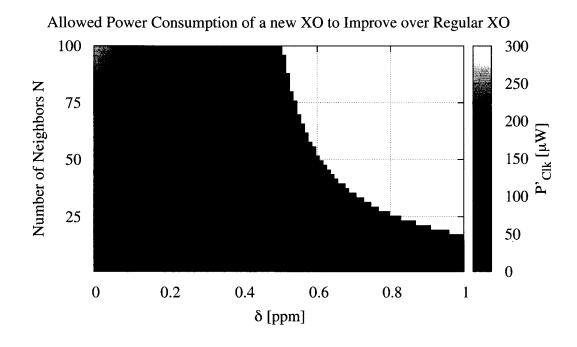

| 5.3 | Result of Equation 5.6 using the Epic platform as an example. We can       |     |

|-----|----------------------------------------------------------------------------|-----|

|     | observe that for dense networks ( $N > 75$ nodes), a TCXO with a power     |     |

|     | consumption of around $200\mu W$ starts to be a viable solution to improve |     |

|     | the power consumption                                                      | 109 |

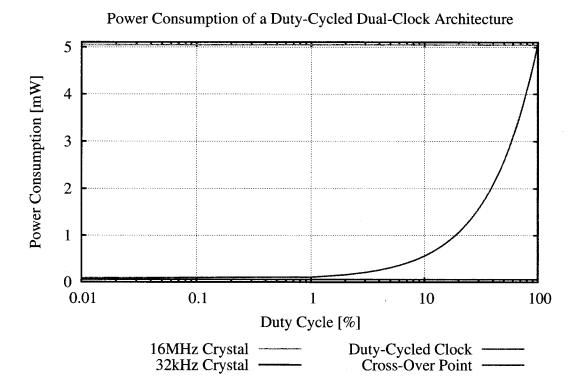

| 5.4 | Power consumption of a dual-clock hardware design given a specific         |     |

|     | duty-cycle of the radio, assuming the slow clock consumes $56\mu W$ and    |     |

|     | the fast clock $660\mu W$                                                  | 111 |

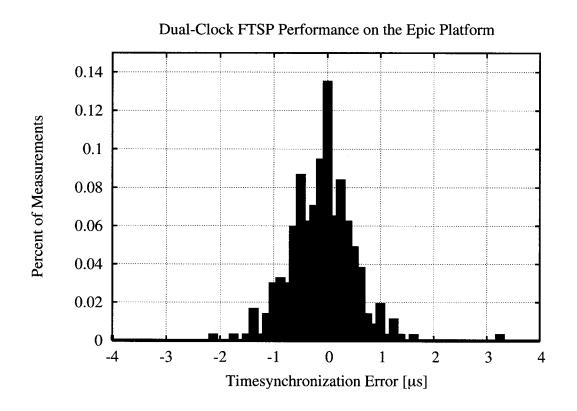

| 5.5 | Performance of a dual-clock enhanced FTSP implementation. The              |     |

|     | hardware contains one 8MHz and one 32kHz crystal. The radio chip is        |     |

|     | a TI CC2420, using the start of frame delimiter (SFD) of the 802.15.4      |     |

|     | messages for time stamping. On average, the accuracy is well below 1       |     |

|     | μs                                                                         | 113 |

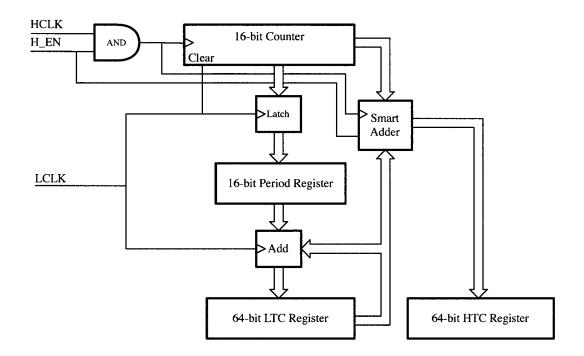

| 5.6 | This is a simplified block diagram of the main HLTimer components.         |     |

|     | The main counter is a 16-bit counter that is fed by the high frequency     |     |

|     | clock signal HCLK. The low frequency clock LCLK drives the rest of         |     |

|     | the logic and increments the different counting registers LTC and HTC      |     |

|     | based on the HLTimer's algorithm                                           | 115 |

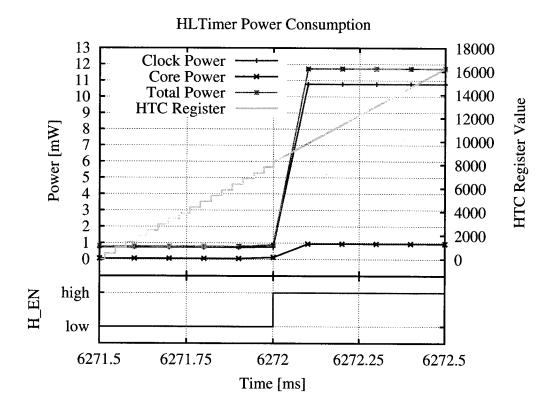

| 5.7 | The power consumption of the HLTimer abruptly increases if the reso-       |     |

|     | lution is set to high. The effect is that the counting in the HTC register |     |

|     | becomes much finer, and thus high resolution time becomes available.       | 117 |

# LIST OF TABLES

| 1.1 | Comparison of different Resonating Elements | •   |

|-----|---------------------------------------------|-----|

| 2.1 | Quantization Effects on Compensation Gain   | 35  |

| 5.1 | Different Time Constants                    | )′. |

| 5.2 | Different Average Power Consumptions        | (   |

#### ACKNOWLEDGMENTS

The title page of this doctoral dissertation contains only one name. However, this dissertation would not have been successful without the help and guidance of many others to whom I am endlessly indebted. I am most especially grateful to my parents, Martha and Heinrich Schmid, for their guidance, support and encouragement to this great challenge. My wife, Sieglinde, for always being there in the good and bad times. My brother and sister, Marcel and Barbara, who's curiousness in my work encourages me to strive further in my research.

During my work at UCLA, I had the fortunate opportunity to work together with some brilliant people and many lifelong friendships have developed in the process. I want to specially thank Young Cho for bringing me on the path of investigating time in embedded systems. I also want to thank Roy Shea, Jonathan Friedman, and Zainul Charbiwala, without who's innumerable discussion, both academic and otherwise, this work would never have achieved the level it did.

I had the privilege of collaborating in many situations with numerous people from other Universities, and even continents. In particular, I would like to thank Martin Vetterli for his encouragement during my time at EPFL to explore another University campus, and his guidance throughout the numerous internships in his laboratory. I am also thankful to Prabal Dutta for the innumerable discussions we had on the importance of time.

Last, but not least, I would like to thank my advisor and mentor, Mani Srivastava. His guidance, breadth of knowledge, and patience with my work never ended to amaze me. He built an extraordinary environment for creativity and innovation at the Networked and Embedded Systems Lab, and I am thankful that he gave me the chance to participate and further the development of my own skills and knowledge within that environment.

# VITA

| 1980         | Born, Arbon, TG, Switzerland.                                                                           |

|--------------|---------------------------------------------------------------------------------------------------------|

| 1985-1987    | Kindergarten, Horn, TG, Switzerland.                                                                    |

| 1987-1995    | Elementary and Secondary School, Horn, TG, Switzerland.                                                 |

| 2000         | Matura, Kantonsschule Romanshorn, TG, Switzerland.                                                      |

| 2002-2003    | Exchange Year McGill University, Montreal, Quebec, Canada.                                              |

| 2004-2005    | Student Researcher at Audiovisual Communications Laboratory (LCAV), EPFL, Lausanne, Switzerland         |

| 2005         | M.Sc. Communication Systems Engineering, Ecole Polytechnique<br>Fédéral de Lausanne (EPFL), Switzerland |

| 2005-present | Graduate Research Assistant, Electrical Engineering Department, UCLA.                                   |

|              | Chancellor's Prize Fellowship                                                                           |

| 2007         | Summer Research Intern, LCAV, EPFL, Lausanne, Switzerland.                                              |

| 2008-2009    | Dissertation Year Fellowship, UCLA                                                                      |

#### **Publications**

- Dustin Torres, Jonathan Friedman, Thomas Schmid, Mani B Srivastava, Software-Defined Underwater Acoustic Networking Testbed, In Proceedings of WUWNET, 2009

- Thomas Schmid, Dustin Torres, Mani B Srivastava, Demo Abstract: Low-power High-precision Timing Hardware for Sensor Networks, (Demo Abstract), In Proceedings of SenSys, 2009

- Thomas Schmid, Zainul M Charbiwala, Roy S Shea, Mani B Srivastava, *Temperature Driven Time Synchronization*, IEEE Embedded Systems Letters, 2009

- Younghun Kim, Thomas Schmid, Zainul M Charbiwala, Mani B Srivastava,

ViridiScope: Design and Implementation of a Fine Grained Power Monitoring System for Homes, In Proceedings of the 11th international conference on Ubiquitous Computing (Ubicomp), 2009

- Jonathan Friedman, Thomas Schmid, Zainul M Charbiwala, Mani B Srivastava, Young H Cho, Multistatic Pulse-Wave Angle-of-Arrival-Assisted Relative Interferometric RADAR, In Proceedings of IEEE Radar Conference, 2009

- Thomas Schmid, Zainul M Charbiwala, Jonathan Friedman, Young H Cho, Mani B Srivastava, Exploiting Manufacturing Variations for Compensating Environment-induced Clock Drift in Time Synchronization, In Proceedings of ACM Sigmetrics, 2008

- Thomas Schmid, Jonathan Friedman, Zainul M Charbiwala, Young H Cho, Mani B Srivastava, Low-Power High-Accuracy Timing Systems for Efficient Duty Cycling, In Proceedings of ISLPED, 2008

xvii

- Thomas Schmid, Zainul M Charbiwala, Jonathan Friedman, Young H Cho, Mani

B Srivastava, The True Cost of Accurate Time, In Proceedings of HotPower, 2008

- Thomas Schmid, Jonathan Friedman, Zainul M Charbiwala, Young H Cho, Mani B Srivastava, XCXO: An Ultra-low Cost Ultra-high Accuracy Clock System for Wireless Sensor Networks in Harsh Remote Outdoor Environments, In Proceedings of ISSCC/DAC, 2008

- Younghun Kim, Zainul M Charbiwala, Akhilesh Singhania, Thomas Schmid, Mani B Srivastava, SPOTLIGHT: Personal Natural Resource Consumption Profiler, In Proceedings of HotEmNets, 2008

- Younghun Kim, Thomas Schmid, Zainul M Charbiwala, Jonathan Friedman, Mani B Srivastava, NAWMS: Nonintrusive Autonomous Water Monitoring System, In Proceedings of The 6th ACM Conference on Embedded Networked Sensor Systems (SenSys), 2008

- David Jea, Jason Liu, Thomas Schmid, Mani B Srivastava, Hassle Free Fitness

Monitoring, In Proceedings of The 2nd International Workshop on Systems and

Networking Support for Healthcare and Assisted Living Environments (Health-Net), 2008

- Jonathan Friedman, Zainul M Charbiwala, Thomas Schmid, Young H Cho, Mani B Srivastava, Angle-of-Arrival Assisted Radio Inteferometry (ARI) Target Localization, In Proceedings of MILCOM, 2008

- G. Troxel, E. Blossom, S. Boswell, A. Caro, I. Castineyra, A. Colvin, T. Dreier, J. Evans, N. Goffee, K. Haigh, T. Hussain, V. Kawadia, D. Lapsley, C. Livadas, A. Medina, J. Mikkelson, G. Minden, R. Morris, C. Partridge, V. Raghunathan, R. Ramanathan, C. Santivanez, T. Schmid, D. Sumorok, M. Srivastava, B. Vincent,

xviii

- D. Wiggin, A. Wyglinski, and S. Zahedi, *Enabling Open-source Cognitively-controlled Collaboration among Software-Defined Radio Nodes*, Computer Networks: The International Journal of Computer and Telecommunications Networking (Special Issue on Cognitive Wireless Networks), 2008

- Kartik Ariyur, Thomas Schmid, Yunjung Yi, Zainul M Charbiwala, Mani B Srivastava, On the Impact of Time Synchronization on Quality of Information and Network Performance, In Proceedings of The Second Annual Conference of the International Technology Alliance (ACITA), 2008

- Thomas Schmid, Roy S Shea, Jonathan Friedman, Mani B Srivastava, *Movement Analysis in Rock-Climbers*, (Demo Abstract), IPSN 2007, 2007

- Thomas Schmid, Oussama Sekkat, Mani B Srivastava, An experimental study of network performance impact of increased latency in software defined radios, In Proceedings of the second ACM international workshop on Wireless network testbeds, experimental evaluation and characterization (ACM WiNTECH), 2007

- Andrew Parker, Sasank Reddy, Thomas Schmid, Kevin Chang, Saurabh Ganeriwal, Mani Srivastava, Mark Hansen, Jeff Burke, Deborah Estrin, Mark Allman and Vern Paxson, Network System Challenges in Selective Sharing and Verification for Personal, Social, and Urban-Scale Sensing Applications, Record of the Fifth Workshop on Hot Topics in Networks (HotNets-V), 2006

- Dustin McIntire, Kei Ho, Bernie Yip, Sasank Reddy, Thomas Schmid, Amarjeet Singh, Winston Wu, and William J. Kaiser, Demonstration of The Low Power Energy Aware Processing (LEAP) Embedded Networked Sensor System, (Demo Abstract), In Proceedings of Information Processing in Sensor Networks (IPSN), 2006

- S. Reddy, T. Schmid, A. Parker, J. Porway, G. Chen, A. Joki, J. Burke, M. Hansen,

D. Estrin, and M. Srivastava, *UrbanCENS: Sensing with the Urban Context in Mind*, Proceedings of The Eight International Conference on Ubiquitous Computing (UbiComp), 2006

- G. Troxel, E. Blossom, S. Boswell, A. Caro, I. Castineyra, A. Colvin, T. Dreier, J. Evans, N. Goffee, K. Haigh, T. Hussain, V. Kawadia, D. Lapsley, C. Livadas, A. Medina, J. Mikkelson, G. Minden, R. Morris, C. Partridge, V. Raghunathan, R. Ramanathan, C. Santivanez, T. Schmid, D. Sumorok, M. Srivastava, B. Vincent, D. Wiggin, A. Wyglinski, and S. Zahedi, *Adaptive Dynamic Radio Open-source Intelligent Team (ADROIT): Cognitively-controlled Collaboration among SDR Nodes*, Proceedings of the First IEEE Workshop on Networking Technologies for Software Defined Radio (SDR) Networks, 2006

- Thomas Schmid, Ted Dreier, Mani B. Srivastava, Software Radio Implementation

of Short-range Wireless Standards for Sensor Networking, (Demo Abstract),

Proceedings of the 4th international Conference on Embedded Networked Sensor

Systems (SenSys), 2006

- Thomas Schmid, Ted Dreier, Mani B. Srivastava, Software Radio Implementation

of Short-range Wireless Standards for Sensor Networking, (Demo Abstract),

Proceedings of the First ACM International Workshop on Wireless Network

Testbeds, Experimental Evaluation & Characterization (ACM WiNTECH), 2006

- T. Schmid, H. Dubois-Ferrire, M. Vetterli. SensorScope: Experiences withh a Wireless Building Monitoring Sensor Network, In The Workshop on Real-World Wireless Sensor Networks (REALWSN), 2005

#### Abstract of the Dissertation

# **Time in Wireless Embedded Systems**

by

#### **Thomas Schmid**

Doctor of Philosophy in Electrical Engineering

University of California, Los Angeles, 2009

Professor Mani B. Srivastava, Chair

Wireless embedded networks have matured beyond academic research as industry now considers the advantages of using wireless sensors. With this growth, reliability and real-time demands increase, thus timing becomes more and more relevant. In this dissertation, we focus on the development of highly stable, low-power clock systems for wireless embedded systems. Wireless embedded networks, due to their wire-free nature, present one of the most extreme power budget design challenges in the field of electronics. Improvements in timing can reduce the energy required to operate an embedded network. However, the more accurate a time source is, the more power it consumes. To comprehensively address the time and power problems in wireless embedded systems, this dissertation studies the exploitation of dual-crystal clock architectures to combat effects of temperature induced frequency error and high power consumption of high-frequency clocks. Combining these architectures with the inherent communication capabilities of wireless embedded systems, this dissertation proposes two new technologies; (1) a new time synchronization service that automatically calibrates a local clock to changes in temperature; (2) a high-low frequency timer that allows a duty-cycled embedded system to achieve ultra low-power sleep, while keeping fine granularity time resolution offered only by high power, high frequency clocks.

xxi

### CHAPTER 1

## Introduction

## 1.1 A Short History of Keeping Time

Modern society relies on the ubiquitous availability of accurate time. Scheduling meeting appointments, lunch breaks, office opening/closing hours, or the availability of certain resources are based on the notion of time. We even teach the youngest members of our society how to read clocks and understand the concept of time [Lle92].

Time-telling has a long history. Around 3500 BC, the Egyptians relied on the sun to tell time. Obelisks and sundials were used in order to tell the approximate time of day. For the longest time, the sun and stars were the only measure of time available to humans.

The first mechanical time keepers did not appear until 1500 BC. Water clocks, some of the first mechanical time keepers, relied on a very simple principle. A tiny hole at the bottom of a big bucket lets water escape from it in a near constant stream of drops. Markings on the inside of the bucket indicate the passing of time. Priests used these primitive time keepers at night to schedule the temple rites and sacrifices at the correct hour.

It was not until 1583 AD that Galileo Galilei discovered that a pendulum period denotes constant time. This discovery revolutionized the accuracy of time keeping, and a new generation of clocks and watches was soon to follow.

At about the same time, 15th Century naval exploration drove time accuracy research. Finding the latitude of a ship out in the ocean was easily accomplished using a sextant, by measuring the position of the sun at midday, or the stars at night. However, longitude is much more difficult. You need a sextant, and the knowledge of accurate time. Several large accidents with many dead sailors happened back in those days, because captains miscalculated their position, and thus drove their boats onto reefs.

For that reason, in 1714, the British government established "The Board of Longitude", and offered a prize of £20,000, equivalent to about \$4,000,000 today, for the person who could localize a ship within 30 nautical miles. To achieve such a high accuracy, you needed a clock that could keep time to within 3 seconds per day. Something not possible with the primitive clocks available thus far.

It wasn't until 1736, when John Harrison, a self-educated English clockmaker, tested his marine chronometer "H1" at sea. The H1 successfully calculated the landfall of a ship, though the British Board of Longitude required a trip to America, in order to get the full prize money. Harrison didn't stop after the H1. With each iteration, Harrison improved the accuracy, and especially the size, of the previous model. However, the Board of Longitude never accepted his clock as "accurate enough", and thus never awarded the prize money to Harrison. As a matter of fact, the Board never awarded the prize to anyone, before it was dissolved in 1828, when the significant problem of determining the longitude was considered solved.

Two more radical inventions in the technology of time keeping had a similar effect on the precision of time. In 1918, Alexander M. Nicholson at Bell Telephone Laboratories patented the first crystal controlled oscillator, and in 1955, Louis Essen built the first caesium-133 atom based atomic clock at the National Physical Laboratory in the UK. Both these developments consisted of huge gains in time accuracy, and we wouldn't have the plethora of different devices today without these two achievements.

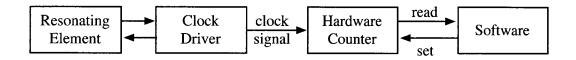

Figure 1.1: Basic block diagram of a clock circuit and associated timer hardware.

For a more detailed early history of time, please refer to the excellent book from Kristen Lippincott, "The Story of Time" [Lip99] and David Allans "The Science of Timekeeping" [AAH97].

## 1.2 Accurate Time in Modern Embedded Systems

Time in embedded systems is usually kept by a specialized sub-system illustrated in Figure 1.1. A periodic *clock signal* lies at the core of the system. The clock signal increments a hardware counter every 1/f seconds, where f is called the frequency of the clock signal. Therefore, at any time t since the n-bit counter was reset, the counter reads  $c(t) = \lfloor f \cdot t \rfloor \mod 2^n$ . The floor operator  $\lfloor \rfloor$  comes into play due to the digital nature of the hardware counter. The 1/f rate at which the counter is incremented is called the *resolution*. However, high resolution is not useful if the software cannot read the counter at that speed. Therefore, the smallest increment at which an application can read the counter is called *precision*. Finally, the counter is typically set to an international time calendar, e.g. UTC. The *accuracy* determines how true the counter holds to that calendar.

The clock signal is a periodic signal with some nominal frequency  $f_0$ . Every clock signal will deviate from its intended nominal frequency for both dynamic (environmental changes, like pressure, temperature, acceleration) and static (imprecision in its manufacture) reasons. This deviation is termed *frequency error* (or inversely *frequency*

stability) defined as  $f_e(t) = f_0 - f(t)$ , where f(t) is the frequency of the clock signal at time t. In general, this error is very small and is commonly expressed in a unitless quantity parts per million (ppm) derived from Equation 1.1.

$$f_e(t) = \frac{f(t) - f_0}{f_0} \cdot 10^6 \tag{1.1}$$

The frequency error of a clock signal changes over time. This change, called frequency drift, can be classified into two categories: short term (seconds to days) and long term (weeks to years). The observable short term changes are due to changes in the environment. Rapid acceleration, like in rockets, or changes of temperature and pressure on the circuit induces frequency change in the order of tens to hundreds of ppm. Long term changes occur as the clock ages. The physical stress induced on components over time can change their electrical properties, and thus introduces a frequency error on the order of a few ppm every year.

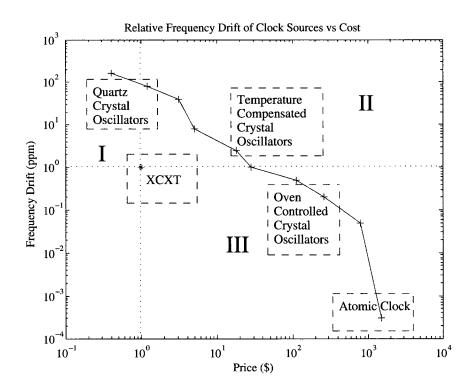

Figure 1.2 shows how the stability of a clock source is related to its price. The x-axis could represent other cost parameters as well, such as power consumption and/or size without appreciable change. To give a perspective on the values of drift, a 10ppm clock source would introduce a measurement error of over 5 minutes over a year. A 0.1ppm clock source on the other hand would be off by only about 3 seconds over a year.

The behavior of the frequency error largely depends on the underlying technology used to generate the clock signal itself. In general, two components are necessary to create a clock signal, a resonating element, and a clock driver. The resonating element is responsible to create an oscillation. The element by itself however does not sustain the oscillation and a clock drive circuit is necessary to initiate and sustain that oscillation. More specifically, it provides both feedback (must meet the Barkhausen [HC04] criteria with  $gain \geq 1$ , total loop phase  $\geq 2\pi$ ) and isolation to the resonator. Although the

Figure 1.2: Relative Frequency Drift vs Cost of commercially available clock sources. Data gathered from different vendors in Fall 2007.

ideal driver varies by oscillator technology, CMOS buffers or inverters are generally well-suited since they have high input impedance (except w.r.t. the low impedance of quartz crystals excited into series resonance), high gain, and high bandwidth.

The choice of inverter, buffered or unbuffered, and the number of inverters in the feedback loop influences the characteristics of the clock signal, its drive strength, and the total power consumption of the clocking circuit. Often times, the clock driver is either integrated with the resonating element (usually called an oscillator) or it resides within the microprocessor. In the first case, the driver will have high drive strength in order to deliver a high quality clock signal to many different digital components, though it will consume a lot of power. In the second case, the clock driver is matched to the internal clock signal network of the microprocessor, and thus is optimized for power consumption. For example, a clock oscillator from Abracon at 16MHz consumes about 8.0mW while clocking a Texas Instrument MSP430 Microprocessor. This is about 20% more energy than if we clock the MSP430 directly using a resonating element (Citizen 16MHz crystal) and its internal clock driver, which we measured at 6.1mW.

The frequency error introduced by changes in the clock driver are usually not significant. It is in large part due to physical changes in the resonating element that the frequency of the clock signal changes over time. Therefore it is important to know the different technologies that can be used as resonating elements, since each of them has different performance characteristics. Table 1.1 summarizes the characteristics of the most common resonating elements, and the next subsections will briefly introduce each one of them.

#### 1.2.1 LC/RC Circuits

One of the simplest resonating elements is an LC-circuit, consisting of one inductor (L) and one capacitor (C). An electric current can resonate between the two elements

| Туре               | Stability            | Power           | Cost                       |

|--------------------|----------------------|-----------------|----------------------------|

| LC/RC              | 1000's of ppm        | Low             | Cents to free              |

| Ring Oscillator    | 1000's of ppm        | Low             | Cents to free              |

| Crystal            | 10's of ppm          | Low - High      | 10's of cents to Dollars   |

|                    | <1ppm if controlled  | Freq. Dependent |                            |

| Crystal Oscillator | <1ppm to 10's of ppm | Med - High      | Dollars to 10's of Dollars |

| MEMS Resonator     | 10's to 100's of ppm | High            | 10's of Cents to Dollars   |

Table 1.1: Comparison of different Resonating Elements

at the circuit's resonant frequency  $f=\frac{1}{2\pi\sqrt{LC}}$ . LC oscillators offer comparatively low production cost and can be produced as an integrated circuit on a chip. However, the precision of the value of L and C and the effect of temperature on these values make this resonating element highly frequency unstable. Frequency errors in the order of thousands of ppm can be easily observed. LC circuits are now rarely used for modern digital applications.

A similar circuit can be produced using a resistor (R) and a capacitor (C). Its advantage over an LC resonator is a cheaper on-chip integration, because an inductor is large to produce compared to a resistor, and area on a chip costs money. Many modern microprocessors integrate such RC-type oscillators as a cheap alternative to external resonators. The Texas Instruments MSP430 families or the Atmel SAM3U are two such example. Like the LC circuit, the RC circuit uses passive components that are subject to similar degrees of inaccuracies. Thus, both resonators are only used in digital circuits where the frequency stability is not critical, like clocking the main CPU. One advantage of RC oscillators is their fast startup times of only a few  $\mu$ seconds. This fast startup can lead to considerable power savings in duty-cycled systems.

#### 1.2.2 Ring Oscillator

A ring oscillator is a device consisting of an uneven number of logical NOT gates. Each NOT gate has a specific transition time. Connecting an uneven number of them into a loop generates a clock signal with a frequency of  $\frac{1}{n \cdot \tau}$  where  $\tau$  is the transition time of one inverter. Thus, the frequency of a ring oscillator can be changed by revising the number of NOT gates in the circuit.

An advantage of ring oscillators is their very low price. Ring oscillators can even be synthesized in a FPGA. However, the frequency accuracy of a ring oscillator is very bad because the transition time of each NOT gate depends heavily on the applied voltage and temperature of the circuit. Frequency error is typically on the order of thousands of ppm. While the frequency drift of a ring oscillator is comparable to that observed in LC/RC circuits, a ring oscillator is typically smaller, cheaper to implement for integrated devices, and has a better output signal. Hybrid designs of ring oscillators and some sort of RC-oscillator can be found in some applications where the actual frequency isn't critical and where a cheap oscillator is necessary or desired.

#### 1.2.3 Quartz Crystal

Quartz crystals are probably the most common resonating elements in today's digital systems. They are cheap and have a very stable frequency. The main working of the quartz crystal is a piezo-electric effect. Applying a voltage to a quartz crystal causes the crystal to mechanically deform, and vice-versa, if the quartz crystal is mechanically deformed then one can measure a voltage. By cutting a quartz crystal at a specific angle from its blank, very selective resonance frequencies can be obtained. There are many different ways of cutting these blanks, ranging from AT-cut, the doubly rotated SC-cut, to Y-cut. Each one of these cuts has specific properties, reacts differently to changes in

Figure 1.3: Picture of a tuning fork 32kHz crystal commonly found in embedded systems to keep wall time. They are small, and consume  $< 15\mu W$ .

the environment, and has different aging characteristics.

The primary causes of aging are mass transfer to or from the resonator's surfaces due to absorption or desorption of contamination, changes in the oscillator circuitry, and atomic level changes in the quartz material. Therefore, in order to achieve low aging, crystal units must be fabricated and hermetically sealed in an ultra-clean, ultra-high-vacuum environment. The aging rates of typical commercially available crystal oscillators range from 5ppm-10ppm per year for an inexpensive crystal, to 0.5ppm-2ppm per year for a temperature-compensated crystal, to 0.05ppm-0.1ppm per year for a temperature-controlled crystal [Vig92].

The most common low-frequency quartz crystals, up to about 100kHz, are the so called tuning fork crystals. They are called tuning fork because they have the same Y-shape and vibrate similar to a musical tuning fork. See Figure 1.3 for an example. The tuning fork crystal has a quadratic frequency error curve reaction to changes in temperature that ranges from about -120ppm to 10ppm, reaching the maximum at about room temperature. These crystals are commonly used in real time clocks to keep wall time during system sleep, because they consume very little power ( $< 15\mu W$ ).

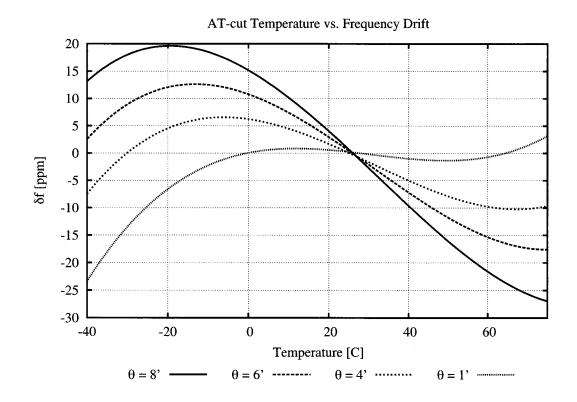

For higher frequencies, AT-cut crystals account for up to 75% of all quartz resonators made, due to their excellent frequency-temperature (f - T) characteristics. They come in frequencies ranging from 1MHz up to several hundreds of MHz. The AT-cut crystal exhibits a cubic frequency error curve reaction to changes in temperature, that ranges from  $\pm 100ppm$  down to  $\pm 20ppm$ , depending on the quality.

To produce a quartz resonator, manufacturers cut out a tiny sheet from a quartz crystal at a specific shear angle. Different angles of cut produce vastly different crystal characteristics. The AT-cut crystal is cut at a nominal angle of  $35^{\circ}20'$ . The f-T characteristics of AT-cut crystals is well studied in the literature and is found to follow

Figure 1.4: Frequency Drift vs Temperature for two AT-cut crystals. The crystals are cut at an angle of  $35^{\circ}20' + \theta$

a third order polynomial using:

$$\delta f_{stability}(T) = A(T - T_0)^3 + B(T - T_0) + C$$

(1.2)

where  $A,B,C,T_0$  are unique to each device. Interestingly, this is the key observation behind the compensation techniques detailed in Chapter 2, the value of B is extremely sensitive to any imprecision in the angle of the cut itself. Figure 1.4 shows how the f-T characteristics vary for AT-cut crystals sheared with a slightly different angle of cut. This slight difference could be either deliberate or due to manufacturing variation. The key idea of Chapter 2 behind improving the stability of the clock source is to exploit this difference in f-T characteristics for two sources to compensate one of them.

#### **1.2.3.1** Compensation Techniques

Different techniques have been developed to make quartz crystals more stable with respect to environmental changes. The biggest effect on frequency stability are changes in temperature. Thus, many compensation techniques reverse this effect by measuring the temperature, and then tuning the crystal to the right frequency. These types of crystals are called Temperature Compensated Crystal Oscillators (TCXO), and there are many possible ways in how to do that [ZZX05]. The most advanced and precise crystals use a microcontroller and a doubly rotate SC-cut crystal. SC-cut crystals have the interesting behavior that they can be excited at two different frequencies at the same time. Since both frequencies have a different temperature stability curve, by measuring both frequencies in the microcontroller the output frequency can be tuned without directly measuring the temperature using a thermistor. This type of crystal is called Microcomputer Compensated Crystal Oscillator (MCXO [BMH89]). The major limiting factor on the attainable frequency stability of the TCXO or MCXO is hysteresis [KV90]. The lowest observed stability using the 10MHz/3.3MHz dual-mode MCXO was 1 part per billion (ppb). However, more typical TCXO's will have a limit of around 0.1 ppm. TCXOs can often be found in GPS applications, however their prohibitive high cost of \$10 to \$100 and the non-negligible power consumption makes them less appealing to general usage in wireless sensor networks.

Another possibility for temperature compensation is keeping the crystal at a stable temperature using an oven, instead of measuring the temperature. This type of crystal is called an Oven Controlled Crystal Oscillator (OCXO), and can achieve a stability of 1 to 5 ppb. However, that stability comes at a huge cost of energy, which typically ranges between 1 to 5 Watt. Such a high energy profile is clearly not suited for sensor networks. OCXOs are usually found in cellular phone basestations, where the high accuracy is needed for wireless communication purposes.

#### 1.2.4 MEMS Resonators

One of the latest developments are Microelectromechanical System (MEMS) Resonators. The first MEMS resonators were built in 1967 [NNW67], though only recently became available to the general public. An advantage of the MEMS resonator is the possibility to directly integrate them into the CMOS process and thus allow a smaller PCB layout and better integrated systems. However, their power consumption is considerably higher than the power used for regular crystal oscillators. For example, we measured the power consumption of the SiTime 8002AI 16MHz MEMS Oscillator at 41mW without any digital circuit connected to it. This power consumption is outside of the realm of wireless sensor networks, though we can expect these power numbers to fall over the next few years, while MEMS resonators evolve further in research and are tailored towards low-power applications [RKM05].

#### 1.2.5 Other Types of Resonators

There are a multitude of resonating elements that we have not yet discussed. Ceramic resonators, bulk acoustic wave (BAW) resonators, rubidium oscillator, atomic clocks, or opto-electronic oscillators can all be used to generate clock signals. These resonating elements are not a good fit for wireless sensor network applications because of their bad frequency stability, high price, or prohibitive power consumptions.

Research in resonators is still very active, and maybe someday every embedded device may contain an atomic clock itself. For Example, the National Institute of Standards and Technology (NIST) is working on a chip-scale atomic clock [KSS05]. It still consumes too much power (195 mW) to be a viable solution for sensor networks though one day this might be low enough to be put in each and every sensor device.

# 1.3 Contributions

The focus of this dissertation is on the investigation of a key source of timing error — the local clock (in)stability. Traditionally, this has required the use of expensive clock sources that are not cost or energy effective in low-end wireless sensor nodes. Besides developing novel clock sources, we can't forget about the inherent networked nature of wireless sensor networks, and thinking about ways of exploiting these aspects.

Our objective is to develop a new timing source for sensor networks using a novel cross-layer approach. The first contribution of this dissertation is a new way of temperature compensating a crystal oscillator using a technique called *Differential Drift*. As we will show in Chapter 2, this algorithm can outperform regular temperature compensated crystal oscillators by exploiting manufacturer variations in crystal oscillators. However, the Crystal Compensated Crystal based Timer (XCXT) does not exploit any communication capabilities of a sensor network platform, and thus still has to be factory calibrated during production.

The second contribution of this dissertation is a thorough investigation of the effects of temperature on networked time synchronization. In Chapter 3 we show why the common assumption of static drift during resynchronization intervals doesn't always hold true, and that time synchronization performance can drastically be impacted by the change of environmental temperature. Through the lessons learned from this investigation, Chapter 3 describes a new time synchronization protocol called Temperature Compensated Time Synchronization, which exploits the often present on-chip temperature sensor. With this additional knowledge, a node can elongate its resynchronization interval, and thus save energy and communication overhead.

The last contribution of this dissertation is the development of hardware architectural support for ultra low-power and high time-resolution time synchronization. A prototype

implementation of the device showed great promise, pushing wireless embedded time synchronization into a new dimension of sub-microsecond accuracies, with power consumptions close to a regular 32kHz tuning fork crystal. We do hope that this device will augment future sensor network architectures to provide them with unprecedented high accuracy of time, enabling researchers to improve localization, beam-forming, distributed logging mechanisms, and other algorithms that rely on the availability of highly accurate time.

# **CHAPTER 2**

# **Dual Crystal Designs for Temperature Induced**Frequency Error Compensation

## 2.1 Introduction

The single biggest impediment to a node's battery-powered lifetime is the energy spent during radio communication, and secondary to that, the time spent in its "awake" (as opposed to its low-power shutdown "sleep" state). Reduce these times, and lifetime improves substantially. However, as soon as nodes in the network begin sleeping and are correspondingly offline, other nodes in the network that are still awake can no longer use them as a communications hub to route sensor data back to a command-and-control station (referred to as a "gateway" node). To optimize sleep time and network performance simultaneously all of the nodes must synchronize their internal clocks and sleep and wake at the same time (we are aware that this statement is somewhat of a generality and numerous works on WSN scheduling exist, but our axiom to follow—that better synchrony yields better lifetime—still holds in these cases).

Commodity time references in WSN's, and indeed consumer and industrial products in general, typically consist of a quartz crystal driven by a Colpitts oscillator. This configuration is popular because it offers substantially better performance than switched resistive-capacitive networks and ceramic-based mechanical resonators at a moderate and tolerable marginal cost (see Figure 1.2). However, crystals drift in frequency as

their temperature changes. A survey of available HC-49S packaged crystals reveals that the majority of inexpensive parts experience a drift over the commercial temperature range (-20°C, +70°C) of ± 50ppm. With this much deviation, nodes must spend at least 0.01% of their lifetimes awake [DCS07] in-order to guarantee that when they transmit, their intended receiver (whose clock has drifted differently) is awake to receive the broadcast. While this may sound acceptable, consider that a node that wants to sample water quality once per hour may only require a total of 100ms to wake, take the measurement, communicate any findings, and return to sleep. This corresponds to spending as little as 0.0028% of its lifetime awake. Repairing the temperature-imposed drift in the crystal-based clocks could improve network lifetime more than 3.5 times!

This chapter describes a novel clock system (hardware and software) that is composed of two crystal oscillators running in parallel at each node. It exploits the subtle manufacturing differences in each crystal that produce different drift-vs.-frequency behaviors. By measuring this difference it compensates for the drifting clock. In effect, it uses one crystal to compensate the other. We call this system as a whole the XCXT (Crystal Compensated Crystal based Timer). The notion of a timer comes from the subtle difference to regular oscillators or clocks. It provides not a corrected frequency (like a TCXO would), but rather it provides a corrected timer to a microcontroller. However, the XCXT architecture could easily be extended such that it provides a stable 1pps signal to an other device, which it already uses internally for corrections.

#### 2.1.1 Related Work

Before we describe the software based compensation technique, it is noteworthy to mention the state-of-the-art in oscillator design. For mid-performance applications, like GPS receivers, designers prefer to use a temperature compensated crystal oscillator or TCXO [NB63, NH68b, ZZX05]. The approach followed by a TCXO manufacturer is to

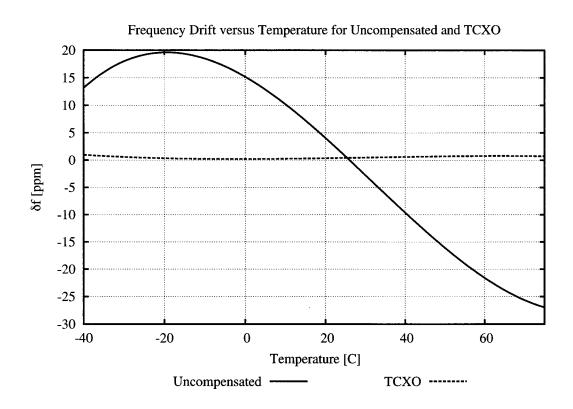

Figure 2.1: Frequency Drift vs Temperature for an uncompensated AT-cut quartz crystal oscillator and temperature compensated crystal oscillator (TCXO).

characterize each device in the factory to obtain its f - T curve [SC01]. Then, by using a custom analog matching circuit [KS96] or a digital tuning circuit with a temperature sensor [CCD89, LHH00, LHT05], the f - T characteristics are corrected by minuscule frequency adjustments to negate the effects of drift. Figure 2.1 shows the improvement in the drift performance of a commercially available digital TCXO [Max08] over an uncompensated oscillator. For high-performance applications, like GSM or CDMA cell phone basestation towers, designers employ an oven controlled crystal oscillator or OCXO which has an active mechanism of maintaining the temperature of the crystal structure, allowing much higher frequency stability over external temperature variations at the cost of an active heating element.

## 2.1.2 Novel Approach

The basic idea of Differential Drift (see Section 2.2), i.e., exploiting two components to compensate its frequency drift for each other, isn't entirely new. In [Sch] Schodowski introduces a temperature sensing device using a dual-harmonic-modecrystal (SC cut crystal). The two harmonics of the SC cut crystal have different temperature behavior. Mixing these two frequencies results in a beat frequency that is proportional to the temperature. Subsequently, Bloch et al. [BMH89] develop the Microcontroller Compensated Crystal Oscillator (MCXO) based on said SC cut crystal. This MCXO achieves the precision of an Oven Controlled Crystal Oscillator (OCXO) although it consumes only a fraction of its power (~70mW instead of ~1.5W) since it doesn't need an active heating element.

Measuring the temperature using two AT-cut crystals, which is similar to our basic approach of measuring drift, has been done by Satou et al. [SH93]. Nevertheless, all the prior work focuses on ways to generate a stable frequency for the purpose of building accurate oscillators. This research on the other hand does not begin with the sole interest

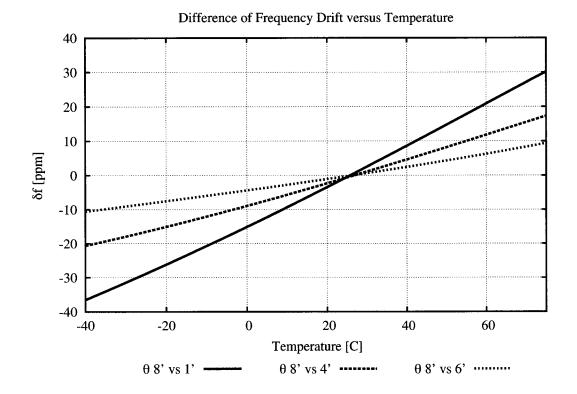

Figure 2.2: Differential Frequency Drift vs Temperature for multiple pairs of differently AT-cut oscillators. Note that the steeper the slope, the better it is for our compensation algorithm.

of building a low drift oscillator. Instead, we sought to find a way to provide accurate time when an application requests it.

The contribution of this chapter are the low-power timer algorithms for wireless sensor network applications, and a full working prototype that achieves a  $5\times$  better energy performance compared to commercially available systems, with the potential of higher gains in future hardware iterations.

# 2.2 Introducing Differential Drift

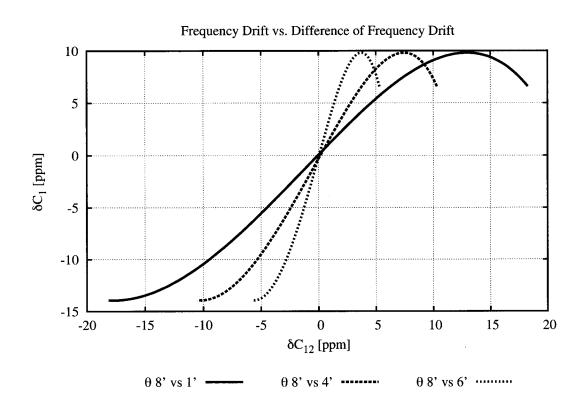

In order to explain how the software based compensation technique works, we first describe the mechanism intuitively. Assume that the system under consideration has two AT-cut quartz crystal oscillators with slightly different shearing angles. For now, we pick the crystals with the top and bottom curves from Figure 1.4 representing the  $35^{\circ}21'$  cut and the  $35^{\circ}28'$  cut. Measuring the "difference of drift" between the two oscillators (or differential drift) over the entire temperature range and plotting it against temperature, we obtain Figure 2.2. The reason that Figure 2.2 is almost a straight line is due to the fact that between the two crystals, it is the B parameter from Equation 1.2 that dominates. Now, if instead we plot the frequency drift of one of the oscillators against the differential drift, we obtain Figure 2.3, which is similar to the f - T curve of that oscillator. This leads us to believe that if the system measures the differential drift at run time, it can estimate the relative drift of one of its oscillators. Using this information, the system can make a correction to its oscillator when it deviates and thus gain higher frequency stability.

This approach is analogous to traditional temperature compensation techniques except that there are two significant advantages to compensating using differential drift. On the one hand, temperature sensing is itself error-prone, requiring its own calibration and compensation system to provide an appreciable accuracy in the reading. Further, temperature sensing displays non-linear dynamic behavior causing hysteresis effects during temperature variations. On the other hand, the measurement of differential drift is completely done in digital logic and software, and the accuracy of measurement can be set arbitrarily high. There are no dynamic behaviors that affect the reading and the speed of acquiring a reading scales with the speeds of deep sub-micron process technology. Additionally, the potential saving in hardware and thus production cost is tremendous since the logic circuitry could directly be integrated into microcontrollers or

Figure 2.3: Frequency Drift versus Difference of Frequency Drift for several pairs of AT-cut oscillators. The larger the full span of  $\delta f_{12}$  the better our algorithm can compensate.

systems on a chip (SoC) at virtually no additional cost. To put it briefly, using simpler hardware with smarter algorithms can benefit in lower production cost and performance advantages, as will be show later on.

# 2.3 The Crystal Compensated Crystal-Based Timer (XCXT)

The crystal compensated crystal-based timer uses measurements of differential drift introduced in Section 2.2 to compensate for the frequency deviation of the clock source. The following illustrates how this is done. Let the frequency of the two oscillators in the system be denoted as  $f_1$  and  $f_2$ . These frequencies deviate due to various factors from the nominal oscillation frequency of  $F_0$  Hz. The relative frequency drift for each oscillator is given by Equation 1.1. The differential drift, defined in Section 2.2 and denoted as  $\delta f_{12}$ , is given by  $\delta f_{12} = \delta f_1 - \delta f_2$ . To measure the differential drift, observe that  $\delta f_{12}$  can be simplified using Equation 1.1 to:

$$\delta f_{12} = \frac{f_1 - F_0}{F_0} - \frac{f_2 - F_0}{F_0} = \frac{f_1 - f_2}{F_0} \tag{2.1}$$

Thus, measuring differential drift could be implemented by measuring the difference in frequencies between the oscillators. Measuring frequencies in software is achieved by counting the number of clock pulses within some fixed time interval and dividing by that interval. The interval must be large enough so that the 1/f temporal quantization error does not affect the accuracy of the measurement. On the other hand, the interval must remain small to ensure short measurement acquisition times and quick response to dynamic environments. The sampling interval could be derived from a faster clock source in the system by generating a low frequency sampling signal  $F_s$ .

The frequency correction algorithm is executed in two parts, a one time calibration phase and a run time compensation phase. The simplest implementation of the algorithm requires the software to have low level access to a hardware timer and two hardware

counters. However, it is very likely that this restriction can be relaxed to one counter in future implementations.

#### 2.3.1 Calibration Phase

In the calibration phase, the system develops an equivalent of the  $\delta f_{12}$  vs.  $\delta f_1$  characteristics by measurement against a known reference of the sampling clock,  $F_s$ . The calibration phase is performed for a pair of oscillators at the factory. This is analogous to the calibration phase performed for TCXOs described earlier, except that the calibration reference required is simply a stable externally applied sampling clock,  $F_s$ . The requirement to accurately measure temperatures is eliminated. The calibration phase requires the use of two free running hardware counters  $C_1$  and  $C_2$  that are being fed from the two oscillators with frequencies  $f_1$  and  $f_2$  respectively. The system then captures the values of both counters at the positive edge of  $F_s$  via an interrupt service routine and resets them to zero for the next sample. The collection of counter samples is performed over the largest temperature variation possible, ideally over the entire range from -40 to  $+85^{\circ}C$ . Let the collection of counter samples, sampled at  $F_s$ , be denoted as  $C_1$  and  $C_2$ .

Define two new quantities  $\delta C_i$  and  $\delta C_{ij}$  as follows:

$$\delta C_i = \frac{C_i}{F_0/F_s} - 1 \tag{2.2}$$

$$\delta C_{ij} = \delta C_i - \delta C_j \tag{2.3}$$

Before the sampling routine exits, the routine computes  $\delta C_1$ ,  $\delta C_2$  and  $\delta C_{12}$  and publishes it for subsequent storage. This procedure is shown in the pseudo-code in Procedure 2.1.

It will now be shown that  $\delta f_1 = \delta C_1$ ,  $\delta f_2 = \delta C_2$  and  $\delta f_{12} = \delta C_{12}$ , so that a model of  $\delta C_{12}$  vs.  $\delta C_1$  is equivalent to a model of differential drift  $\delta f_{12}$  versus frequency drift  $\delta f_1$ .

# Procedure 2.1 Calibration:On\_Fs\_Interrupt

C1 ← Counter1.value

$C2 \leftarrow Counter 2.value$

Counter1.reset()

Counter2.reset()

$$dC1 \leftarrow [C1/(F_0/F_s)] - 1$$

$$dC2 \leftarrow [C2/(F_0/F_s)] - 1$$

$$dC12 \leftarrow dC1 - dC2$$

print dC1, dC2, dC12

The value of the counter in each interval can be given by:

$$C_i = \frac{f_i}{F_s} \tag{2.4}$$

where  $f_i$  is the *mean* frequency of the oscillator over the sampling interval.  $\delta f_i$  is given by Equation 1.1 as:

$$\delta f_i = \frac{f_i - F_0}{F_0} = \frac{f_i}{F_0} - 1 \tag{2.5}$$

$$= \frac{C_i \cdot F_s}{F_0} - 1 = \frac{C_i}{F_0/F_s} - 1 \tag{2.6}$$

$$= \delta C_i \tag{2.7}$$

A similar relationship can be shown for  $\delta f_{12}$  and  $\delta C_{12}$ .

At the end of the calibration phase, the system has collected a set of  $<\delta C_{12}, \delta C_1>$  and  $<\delta C_{12}, \delta C_2>$  tuples. We found that these tuples fit well to a third order polynomial function because  $C_{12}$  is linearly proportional to the temperature (see Figure 2.2). Thus, only the values of A, B, C, and D in the following equation are required to be stored:

$$\delta C_1 = A \cdot (\delta C_{12})^3 + B \cdot (\delta C_{12})^2 + C \cdot \delta C_{12} + D \tag{2.8}$$

The entire set of tuples can also be stored as a lookup table, subject to memory availability. Section 2.3.5 describes how this choice affects the performance of the compensation

algorithm.

## 2.3.2 Compensation Phase

The compensation phase performs a continuous frequency correction at run time to provide a higher stability clock. Instead of stabilizing  $f_1$  or  $f_2$  using hardware based tuning circuits, we focus on regenerating a replica of the stable sampling clock,  $F_s$  from the unstable clock sources. It can be shown that the fact that  $F_s$  is at fairly low frequency does not affect the accuracy of the clock as long as it captures dynamic variations in the environment adequately.

The key idea of the compensation algorithm is to estimate the frequency of the sampling clock as closely as possible. Thus, at every pulse of this generated clock, we know that (close to)  $1/F_s$  seconds of real time has elapsed. This value is accumulated in a register that then provides the real time at the pulse edge. To timestamp an event or read time between two pulses, an intermediary correction is required as described in Section 2.3.3.

If the timer is fed the clock source  $f_1$  and loaded with a value  $\gamma$ , the timer expires after a time interval  $\gamma/f_1$  seconds asserting an interrupt. If the timer reloads itself on expiry with the same value  $\gamma$ , it generates a periodic sampling signal with frequency denoted as  $f_{\gamma}$ . Again, two counters  $C_1$  and  $C_2$  are used, fed by the two oscillators running at frequencies  $f_1$  and  $f_2$  respectively.

As shown in the initialization routine in Procedure 2.2, the timer is loaded with a value  $\gamma = F_0/F_s$  since this provides the best initial estimate of the sampling signal. On every timer interrupt, a sampling and compensation routine is executed as shown in Procedure 2.3.