# EFFECTIVE DATA PARALLEL COMPUTING ON MULTICORE PROCESSORS

by

# Jong-Ho Byun

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Charlotte

2010

| Approved by:          |

|-----------------------|

| Dr. Arun Ravindran    |

| Dr. Arindam Mukherjee |

| Dr. Bharat Joshi      |

| Dr. Gabor Hetvei      |

UMI Number: 3439255

# All rights reserved

## INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI 3439255

Copyright 2011 by ProQuest LLC.

All rights reserved. This edition of the work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

©2010 Jong-Ho Byun ALL RIGHTS RESERVED

#### **ABSTRACT**

JONG-HO BYUN. Effective data parallel computing on multicore processors. (Under direction of DR. ARUN RAVINDRAN)

The rise of chip multiprocessing or the integration of multiple general purpose processing cores on a single chip (multicores), has impacted all computing platforms including high performance, servers, desktops, mobile, and embedded processors. Programmers can no longer expect continued increases in software performance without developing parallel, memory hierarchy friendly software that can effectively exploit the chip level multiprocessing paradigm of multicores. The goal of this dissertation is to demonstrate a design process for data parallel problems that starts with a sequential algorithm and ends with a high performance implementation on a multicore platform. Our design process combines theoretical algorithm analysis with practical optimization techniques. Our target multicores are quad-core processors from Intel and the eight-SPE IBM Cell B.E. Target applications include Matrix Multiplications (MM), Finite Difference Time Domain (FDTD), LU Decomposition (LUD), and Power Flow Solver based on Gauss-Seidel (PFS-GS) algorithms. These applications are popular computation methods in science and engineering problems and are characterized by unit-stride (MM, LUD, and PFS-GS) or 2-point stencil (FDTD) memory access pattern. The main contributions of this dissertation include a cache- and space-efficient algorithm model, integrated data pre-fetching and caching strategies, and in-core optimization techniques. Our multicore efficient implementations of the above described applications outperform naïve parallel implementations by at least 2x and scales well with problem size and with the number of processing cores.

#### **ACKNOWLEDGMENTS**

First of all, I would like to deeply thank my advisor Dr. Arun Ravindran for his great support, guidance, patience and encouragement. I would also like to thank Dr. Arindam Mukherjee and Dr. Bharat Joshi for their special help and encouragement. I am also indebted to Dr. Gabor Hetyei for devoting his time to the review of my work.

I would also like to thank David Chassin at Pacific Northwest National Lab (PNNL) for his special support. Specially thanks to all of my friends for their encouragement.

Finally, I deeply thank my dear family; my parents, sisters' families and my aunt's family for their love, support and encouragement. I cannot imagine myself going through all this work without them.

# TABLE OF CONTENTS

| LIST OF FIGURES                          | ix |

|------------------------------------------|----|

| LIST OF TABLES                           |    |

| CHAPTER 1: INTRODUCTION                  | 1  |

| 1.1 Rise of Multicore Computing          | 1  |

| 1.2 Research Goals                       | 2  |

| 1.3 Dissertation Contributions           | 6  |

| 1.4 Dissertation Outline                 | 7  |

| CHAPTER 2: TRENDS IN MULTICORE COMPUTING | 9  |

| 2.1 Introduction                         | g  |

| 2.2 Multicore Architectures              | 10 |

| 2.2.1 Historical Trends                  | 10 |

| 2.2.2 Architectural Elements             | 12 |

| 2.2.3 Case Studies                       | 15 |

| 2.2.3.1 Intel Gainestown                 | 15 |

| 2.2.3.2 Sun UltraSPARC T2                | 17 |

| 2.2.3.3 IBM Cell Broadband Engine        | 19 |

| 2.2.3.4 Nvidia Fermi                     | 24 |

| 2.3 Multicore Programming Tools          | 26 |

| 2.3.1 Parallel Libraries                 | 27 |

| 2.3.1.1 Shared Address Space             | 28 |

| 2.3.1.2 Distributed Address Space        | 29 |

| 2.3.1.3 Stream Processing                | 30 |

|       |                                                                                    | vi |

|-------|------------------------------------------------------------------------------------|----|

|       | 2.3.2 Parallel Languages                                                           | 31 |

|       | 2.3.2.1 Shared Address Space                                                       | 32 |

|       | 2.3.2.2 Partitioned Global Address Space                                           | 32 |

|       | 2.3.3 Parallelizing Compilers                                                      | 34 |

| 2.4   | Multicore System Software                                                          | 34 |

|       | 2.4.1 Shared Memory OS                                                             | 35 |

|       | 2.4.2 Multikernel OS                                                               | 37 |

|       | 2.4.3 Virtualization                                                               | 39 |

| СНАРТ | ER 3: DESIGNING CACHE- AND SPACE-EFFICIENT DATA PARALLEL ALGORITHMS FOR MULTICORES | 40 |

| 3.1   | Introduction                                                                       | 40 |

| 3.2   | Background                                                                         | 43 |

|       | 3.2.1 Computational Models                                                         | 43 |

|       | 3.2.2 Cache-oblivious Model                                                        | 45 |

|       | 3.2.3 Multicore Schedulers                                                         | 47 |

| 3.3   | Parallel Cache-oblivious Design Methodology                                        | 48 |

|       | 3.3.1 Computational Model                                                          | 48 |

|       | 3.3.2 Recursive Geometric Decomposition                                            | 50 |

|       | 3.3.3 Red-Blue Pebble Game                                                         | 51 |

|       | 3.3.4 Nominal Parallel Pebbling Strategy                                           | 53 |

|       | 3.3.5 Weighted-vertex Parallel Pebbling Strategy                                   | 54 |

|       | 3.3.6 Data-aware Scheduling                                                        | 56 |

| 3.4   | Case Studies                                                                       | 58 |

|       | 3.4.1 Matrix Multiplication                                                        | 59 |

|       |                                                                            | vii |

|-------|----------------------------------------------------------------------------|-----|

|       | 3.4.2 Finite Difference Time Domain                                        | 64  |

| 3.5   | Conclusion                                                                 | 69  |

| СНАРТ | ER 4: INTEGRATED DATA PREFETCHING AND CACHING IN MULTICORES                | 71  |

| 4.1   | Introduction                                                               | 71  |

| 4.2   | Background                                                                 | 72  |

| 4.3   | Computation and Data Transfer Parallelism in the IBM Cell/B.E.             | 73  |

| 4.4   | Machine Model and General Bounds                                           | 75  |

| 4.5   | Matrix Multiplication                                                      | 77  |

|       | 4.5.1 Theoretical Bounds                                                   | 77  |

|       | 4.5.2 Discussion                                                           | 86  |

| 4.6   | Finite Difference Time Domain (FDTD)                                       | 88  |

|       | 4.6.1 Theoretical Bounds                                                   | 88  |

|       | 4.6.2 Discussion                                                           | 94  |

| 4.7   | Conclusion                                                                 | 96  |

| СНАРТ | ER 5: EXPERIMENTAL STUDIES IN COMPUTING ON COMMERCIAL MULTICORE PROCESSORS | 98  |

| 5.1   | Introduction                                                               | 98  |

| 5.2   | Experimental Systems                                                       | 99  |

| 5.3   | In-core Optimization Techniques                                            | 102 |

|       | 5.3.1 Matrix-Vector Multiplication                                         | 103 |

|       | 5.3.2 Data Transformation: Data Layout Scheme                              | 104 |

|       | 5.3.3 Loop Transformation: Loop Blocking (Loop Tiling)                     | 108 |

|       | 5.3.4 Loop Transformation: Loop Unrolling                                  | 112 |

|       | 5.3.5 Loop Transformation: Loop Interchange (Computational Reordering)     | 113 |

|       |                                                                            |     |

|                                                                 | viii |

|-----------------------------------------------------------------|------|

| 5.3.6 Vectorization                                             | 115  |

| 5.4 Case Studies: Experimental Results and Performance Analysis | 120  |

| 5.4.1 Dense Matrix Multiplication (DMM)                         | 120  |

| 5.4.1.1 Multicore-efficient Implementation                      | 122  |

| 5.4.1.2 Optimization at Register Level                          | 126  |

| 5.4.1.3 Performance Analysis                                    | 130  |

| 5.4.2 Finite Difference Time Domain (FDTD)                      | 136  |

| 5.4.2.1 Multicore-efficient Implementations                     | 138  |

| 5.4.2.2 Optimization at Register Level                          | 141  |

| 5.4.2.3 Performance analysis                                    | 144  |

| 5.4.3 LU Decomposition                                          | 148  |

| 5.4.3.1 Multicore-efficient Implementations                     | 150  |

| 5.4.3.2 Optimization at Register Level                          | 155  |

| 5.4.3.3 Performance Analysis                                    | 155  |

| 5.4.4 Power Flow Solver based on Gauss-Seidel method (PFS-GS)   | 158  |

| 5.4.4.1 Multicore-efficient Implementations                     | 161  |

| 5.4.4.2 Optimization at Register Level                          | 163  |

| 5.4.4.3 Performance Analysis                                    | 167  |

| 5.5 Conclusion                                                  | 170  |

| CHAPTER 6: CONCLUSION AND FUTURE WORK                           | 173  |

| 6.1 Conclusion                                                  | 173  |

| 6.2 Future work                                                 | 175  |

| REFERENCES                                                      | 177  |

# LIST OF FIGURES

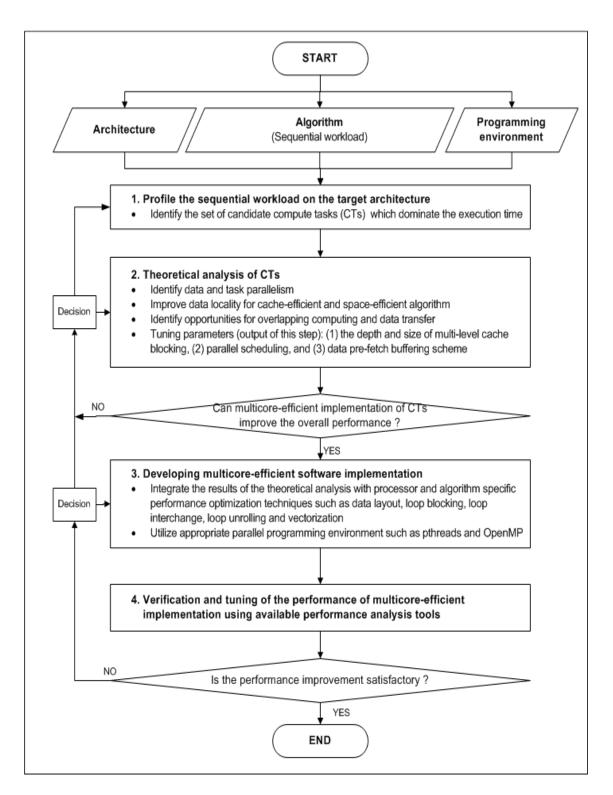

| FIGURE 1.1: | Design flow for multicore-efficient software design.                                                                                                                                                                                                                                    | 4  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

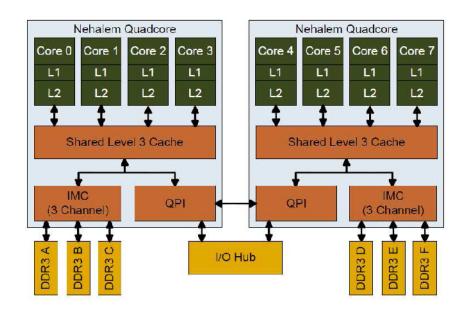

| FIGURE 2.1: | Organization of the Nehalem processors.                                                                                                                                                                                                                                                 | 15 |

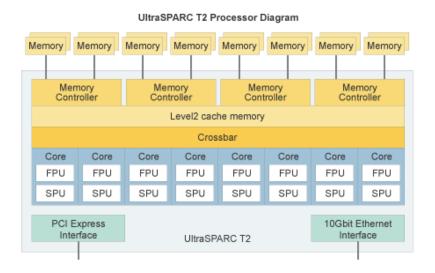

| FIGURE 2.2: | Organization of the UltraSPARC T2 processor.                                                                                                                                                                                                                                            | 17 |

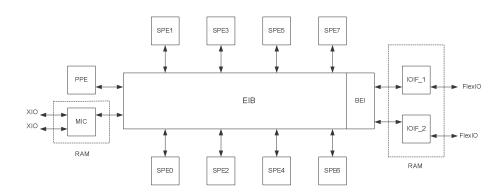

| FIGURE 2.3: | Organization of the Cell Broadband Engine.                                                                                                                                                                                                                                              | 19 |

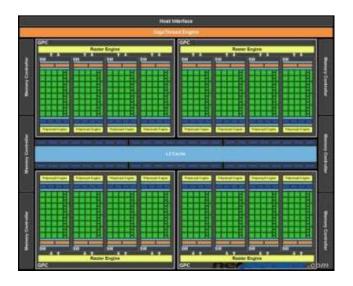

| FIGURE 2.4: | Organization of the Nvidia Fermi.                                                                                                                                                                                                                                                       | 25 |

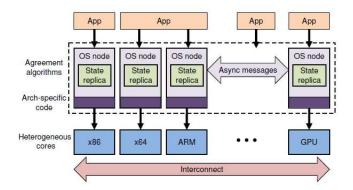

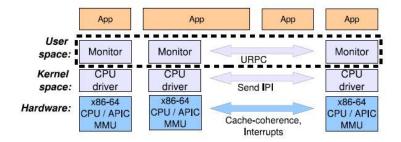

| FIGURE 2.5: | Multikernel model.                                                                                                                                                                                                                                                                      | 37 |

| FIGURE 2.6: | Organization of Barrelfish.                                                                                                                                                                                                                                                             | 38 |

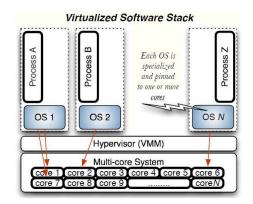

| FIGURE 2.7: | A simplified representation of the virtualized software stack, demonstrating the deployment of a hypervisor and several VMs, each of which is managing a subset of the cores and a subset of the processes.                                                                             | 39 |

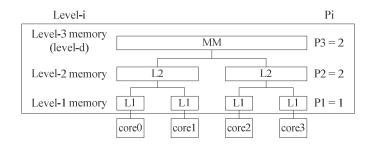

| FIGURE 3.1: | The cache hierarchy of the Intel quad-core Clovertown processor.                                                                                                                                                                                                                        | 50 |

| FIGURE 3.2: | A 2-level geometric decomposition of <i>A</i> , <i>B</i> , and <i>C</i> matrices.                                                                                                                                                                                                       | 60 |

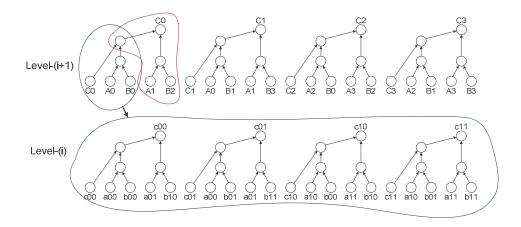

| FIGURE 3.3: | Illustrative level- $(i+1)$ and level- $i$ DAGs for matrix multiplication.                                                                                                                                                                                                              | 60 |

| FIGURE 3.4: | The weighted-vertex pebble game: (a) Initial vertex weight assignment for level- $(i+1)$ DAGs of Figure 3.2 under $\Omega_s$ ; (b) An intermediate step in the pebbling of the level- $(i+1)$ DAGs under $\Omega_s$ .                                                                   | 60 |

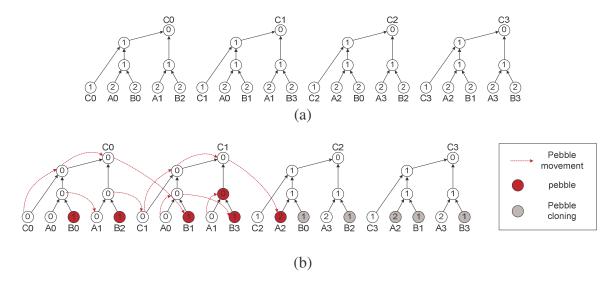

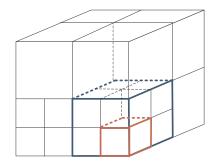

| FIGURE 3.5: | A 2-level geometric decomposition of the <b>E</b> - and <b>H</b> -field cubes.                                                                                                                                                                                                          | 65 |

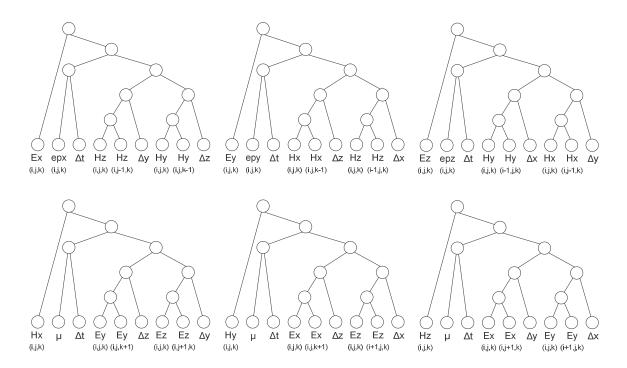

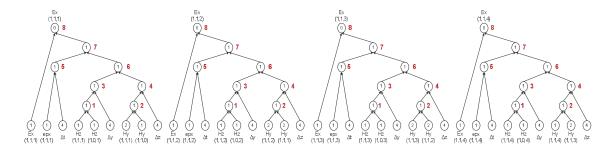

| FIGURE 3.6: | DAGs for FDTD: Note that there are 6 DAGs corresponding to $E_x$ , $E_y$ , $E_z$ and $H_x$ , $H_y$ , $H_z$ .                                                                                                                                                                            | 65 |

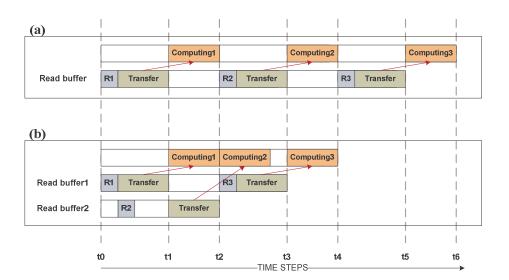

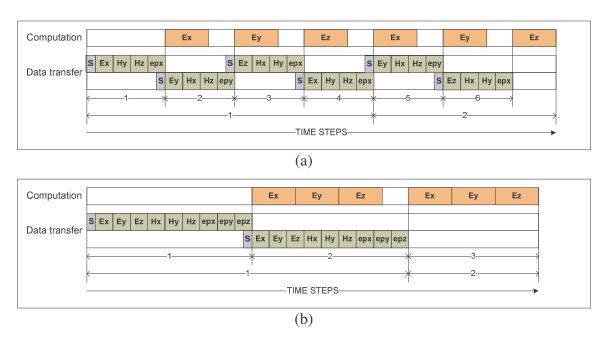

| FIGURE 4.1: | Simultaneous computing and DMA transfer: (a) Execution sequence for single read buffering; (b) Execution sequence for double read buffering.                                                                                                                                            | 74 |

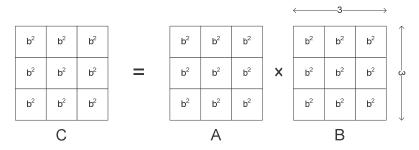

| FIGURE 4.2: | Matrix multiplication with $3\times3$ blocks.                                                                                                                                                                                                                                           | 77 |

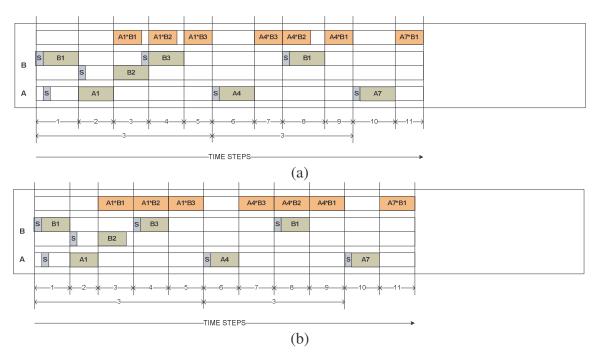

| FIGURE 4.3: | Simultaneous computing and data transfer for single buffer each for matrix $A$ and $B$ : (a) Execution sequence obtained by considering no reuse of the data present in the local memory; (b) Execution sequence obtained by considering reuse of the data present in the local memory. | 79 |

|             |                                                                                                                                                                                                                                                                                         |    |

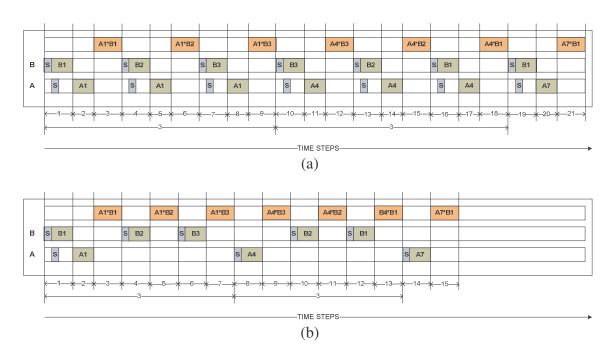

| FIGURE 4.4: | Simultaneous computing and data transfer for single buffer for matrix $A$ and double buffer for matrix $B$ obtained by considering reuse of the data present in the local memory: (a) Data transfer bound case; (b) Compute bound case.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 83  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| FIGURE 4.5: | Simultaneous computing and data transfer for double buffer for both matrix <i>A</i> and <i>B</i> obtained by considering reuse of the data present in the local memory: (a) Data transfer bound case; (b) Compute bound case.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85  |

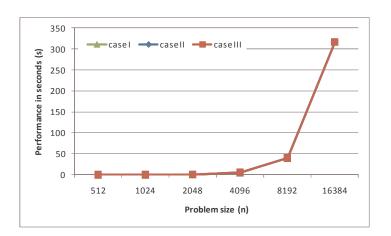

| FIGURE 4.6: | Theoretical lower bounds for matrix multiplication on IBM Cell/B.E.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 88  |

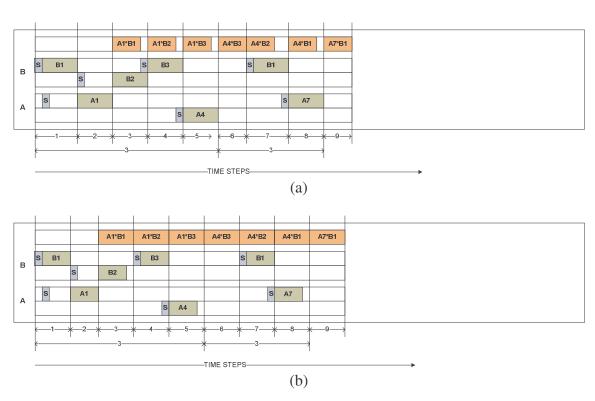

| FIGURE 4.7: | Simultaneous computing and data transfer for single buffer for E-field computation: (a) Execution sequence obtained by considering no reuse of the data present in the local memory. This scheme requires the storage of $4$ blocks of data in the local memory; (b) Execution sequence obtained by considering reuse of the data present in the local memory between $E_x$ , $E_y$ and $E_y$ , $E_z$ . This scheme requires the storage of $4$ blocks of data in the local memory; (c) Execution sequence obtained by considering reuse of the data present in the local memory between $E_x$ , $E_y$ , and $E_z$ . This scheme requires the storage of $5$ blocks of data in the local memory; (d) Execution sequence obtained by considering reuse of the data present in the local memory between $E_x$ , $E_y$ , and $E_z$ but with all the data fetched initially. This scheme requires the storage of $9$ blocks of data in the local memory. | 91  |

| FIGURE 4.8: | Simultaneous computing and data transfer for double buffers for E-field computation as data transfer bound cases: (a) Execution sequence obtained by considering no reuse of the data present in the local memory. This scheme requires the storage of 4 blocks of data in the local memory; (b) Execution sequence obtained by considering reuse of the data present in the local memory between $E_x$ , $E_y$ , and $E_z$ but with all the data fetched initially. This scheme requires the storage of 9 blocks of data in the local memory.                                                                                                                                                                                                                                                                                                                                                                                                       | 92  |

| FIGURE 4.9: | Theoretical lower bounds for FDTD on IBM Cell/B.E.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 96  |

| FIGURE 5.1: | Dell Precision 690 with dual Intel quad-core Xeon E5345.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 99  |

| FIGURE 5.2: | SONY PlayStation3 with one PPE and eight SPEs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100 |

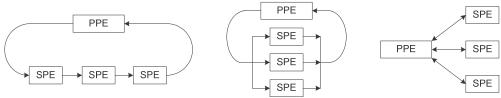

| FIGURE 5.3: | The PPE-centric programming models.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 101 |

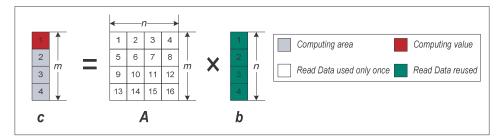

| FIGURE 5.4: | Matrix-vector multiplication with $n=4$ and $m=4$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 104 |

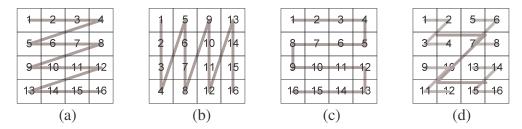

| FIGURE 5.5:  | Data Layout Schemes of $4 \times 4$ Matrix: (a) Row-major order; (b) Column-major order; (c) Space-filling-curve order; (d) Z-Morton order.                                                                                                                          | 104 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

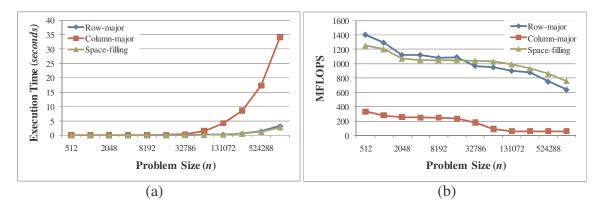

| FIGURE 5.6:  | Performance of data layout schemes for matrix-vector multiplication with fixed $m = 1024$ : (a) The performance in seconds; (b) The performance in MFLOPS.                                                                                                           | 106 |

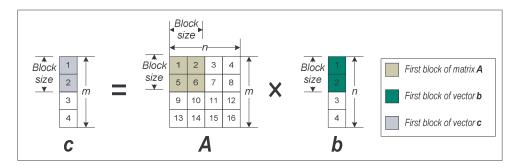

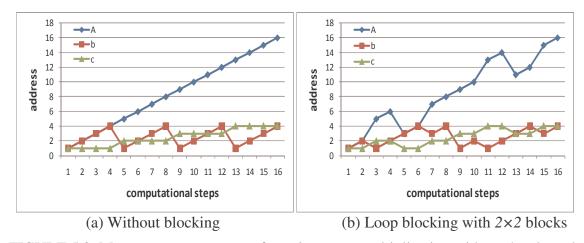

| FIGURE 5.7:  | Implementation of loop blocking algorithm in row-major layout scheme with $n=4$ , $m=4$ and $2\times 2$ blocks.                                                                                                                                                      | 109 |

| FIGURE 5.8:  | Memory access pattern of matrix-vector multiplication with $n=4$ and $m=4$ .                                                                                                                                                                                         | 110 |

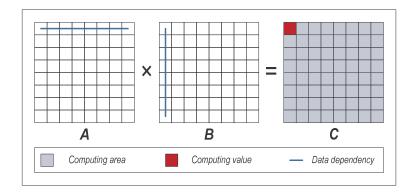

| FIGURE 5.9:  | The data dependency the standard matrix multiplication with $n \times n$ square matrices.                                                                                                                                                                            | 121 |

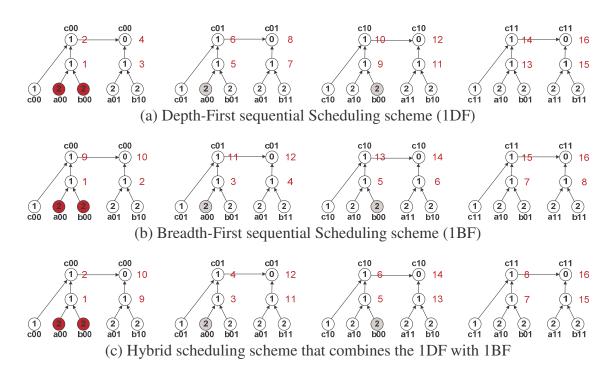

| FIGURE 5.10: | The example of the scheduling schemes on the weighted DAGs at register level blocking with $b_0$ =2; Note, the number on right side of each computational vertex represents the sequential scheduling order.                                                         | 127 |

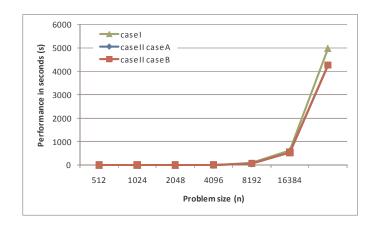

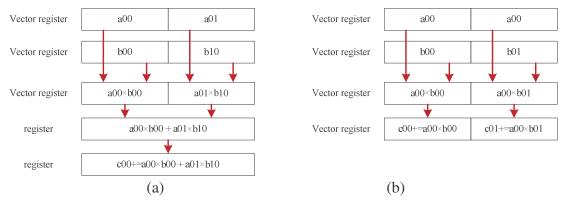

| FIGURE 5.11: | The example of vector computations for two multiplications following by two addition operations simultaneously: (a) Based on 1DF or 1BF scheduling scheme; (b) Based on hybrid scheduling scheme.                                                                    | 128 |

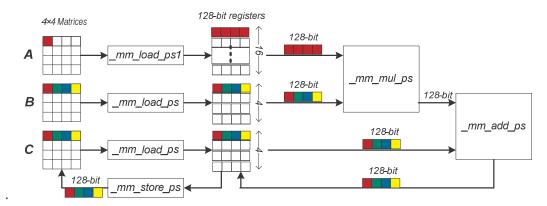

| FIGURE 5.12: | Vectorization implementation at register level blocking with $b_0$ =4 using hybrid scheduling scheme and Intel x86_64 SSE2 intrinsics for Intel Clovertown platform.                                                                                                 | 129 |

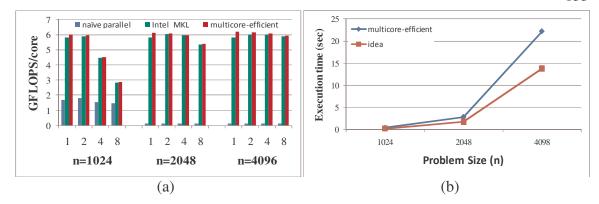

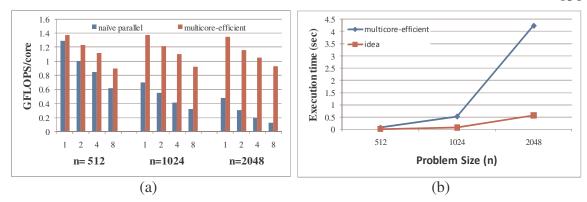

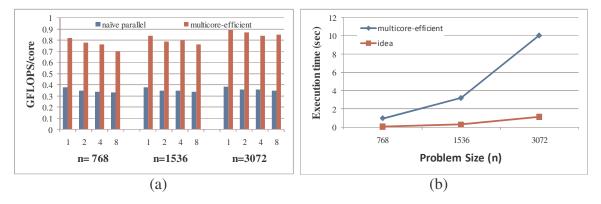

| FIGURE 5.13: | Overall performance on Intel Clovertown platform: (a) Performance in GFLOPS per core; (b) Execution time in seconds on single core.                                                                                                                                  | 133 |

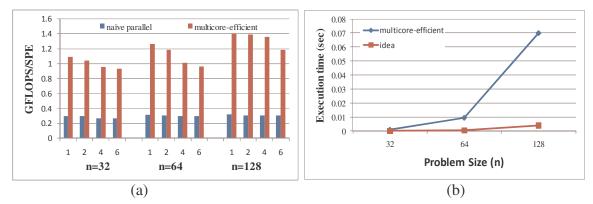

| FIGURE 5.14: | Overall performance on IBM Cell/B.E. platform: (a) Performance in GFLOPS per SPE; (b) Execution time in seconds on single SPE.                                                                                                                                       | 135 |

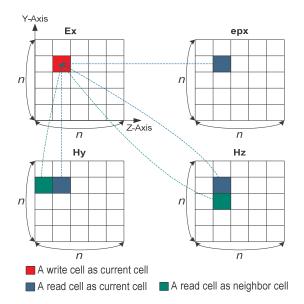

| FIGURE 5.15: | Example of data dependency in space domain for a cell of $E_x$ computation.                                                                                                                                                                                          | 138 |

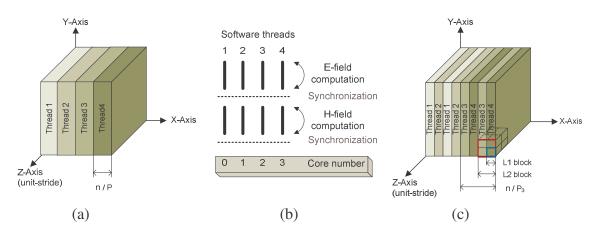

| FIGURE 5.16: | An example distribution of threads among four cores: (a) Data partitioning scheme for the naïve parallel algorithm; (b) Mapping threads to cores for both (a) and (c) data partitioning schemes; (c) Data partitioning scheme for the multicore efficient algorithm. | 139 |

| FIGURE 5.17: | The hybrid scheduling scheme for the four $E_x$ computations for the register level blocking; the number on the right side of each computational vertices indicates the SIMDize scheduling order. | 141 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

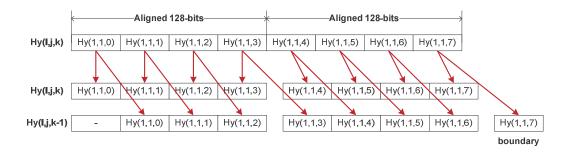

| FIGURE 5.18: | The example of the conflict alignment of 128-bit vector registers for $H_y(i,j,k)$ and $H_y(i,j,k-1)$ .                                                                                           | 142 |

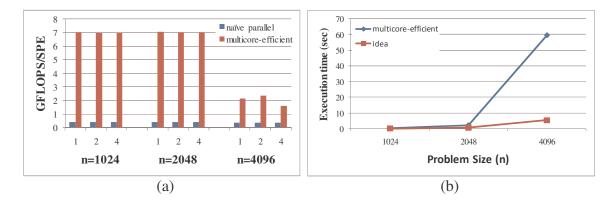

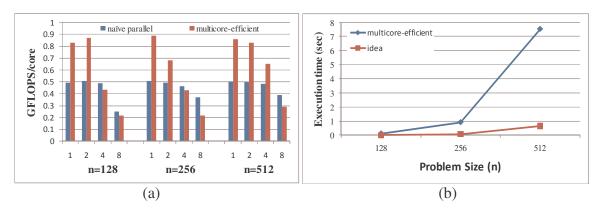

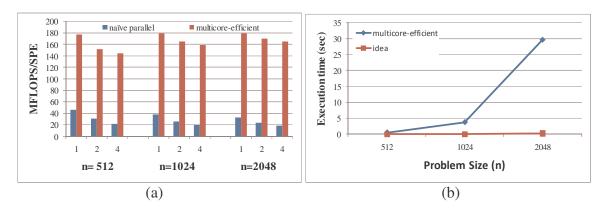

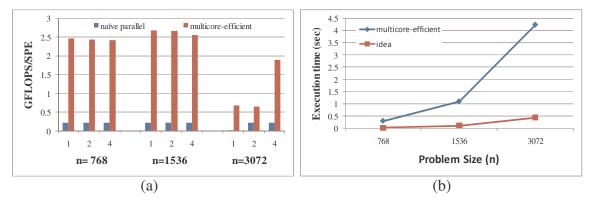

| FIGURE 5.19: | Overall performance on Intel platform: (a) Performance in GFLOPS per core; (b) Execution time in seconds on a single core.                                                                        | 146 |

| FIGURE 5.20: | Overall performance on IBM platform: (a) Performance in GFLOPS per SPE; (b) Execution time in seconds on a single SPE.                                                                            | 148 |

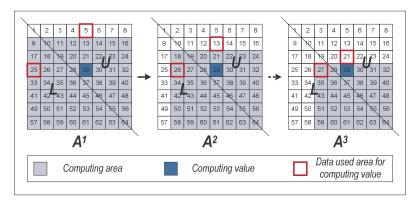

| FIGURE 5.21: | The data dependency of the LU decomposition based on Gaussian elimination method.                                                                                                                 | 150 |

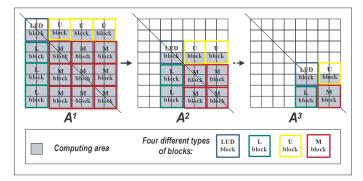

| FIGURE 5.22: | The block partition with the four different types in sub-matrix $A^k$ at d-level.                                                                                                                 | 153 |

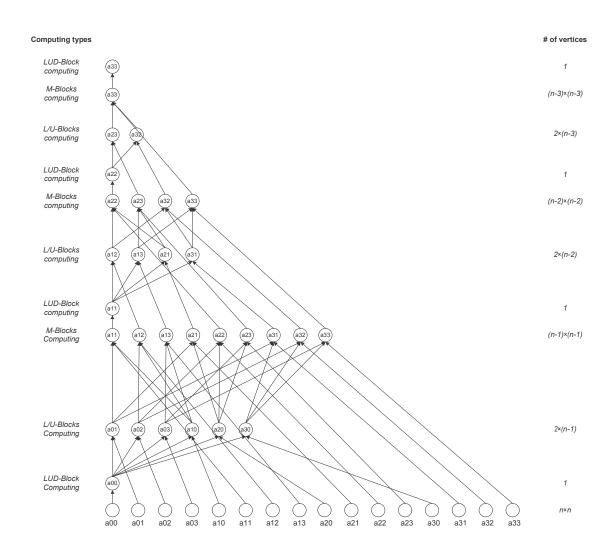

| FIGURE 5.23: | The example of data dependency of LU decomposition for a matrix A with 4×4 blocks.                                                                                                                | 154 |

| FIGURE 5.24: | Overall performance on Intel platform: (a) Performance in GFLOPS per core; (b) Execution times in seconds on a single core.                                                                       | 156 |

| FIGURE 5.25: | Overall performance on IBM Cell BE platform: (a) Performance in GFLOPS per SPE; (b) Execution time in seconds on a single SPE.                                                                    | 157 |

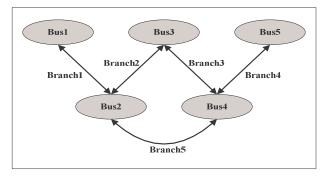

| FIGURE 5.26: | The sample power network computation with 5 buses and 5 branches.                                                                                                                                 | 159 |

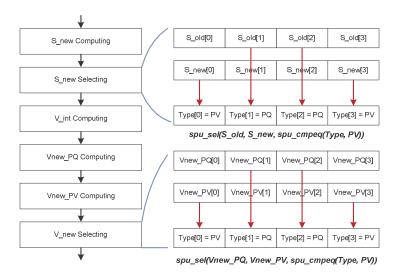

| FIGURE 5.27: | Vectorized Unified-Bus-Computation Module.                                                                                                                                                        | 164 |

| FIGURE 5.28: | Overall performance on Intel Clovertown platform: (a) Performance in GFLOPS per core; (b) Execution time in seconds on a single core.                                                             | 167 |

| FIGURE 5.29: | Overall performance on IBM Cell/B.E. platform: (a) Performance in GFLOPS per SPE; (b) Execution time in seconds on a single SPE.                                                                  | 169 |

# LIST OF TABLES

| TABLE 5.1:  | Pseudo code of the matrix-vector multiplication for different data layout schemes.                                                                                                       | 105 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TABLE 5.2:  | The memory access pattern obtained by following a row-major computational order in the nested loop with the $4\times4$ matrix $A$ laid out in a row-major layout scheme.                 | 107 |

| TABLE 5.3:  | The memory access pattern obtained by following a row-major computational order in the nested loop with the $4\times4$ matrix $A$ laid out in a column-major order layout scheme.        | 107 |

| TABLE 5.4:  | The memory access pattern obtained by following a row-major computational order in the nested loop with the $4\times4$ matrix $A$ laid out in a space-filling curve order layout scheme. | 108 |

| TABLE 5.5:  | An example of matrix vector multiplication with $m \times n$ matrix $A$ using loop blocking $(c = A \times b)$ .                                                                         | 109 |

| TABLE 5.6:  | The performance of loop blocking algorithm with varying block size.                                                                                                                      | 111 |

| TABLE 5.7:  | An example of matrix-vector multiplication with $m \times n$ matrix $A$ using loop unrolling $(c = A \times b)$ .                                                                        | 112 |

| TABLE 5.8:  | The performance of loop unrolling algorithm with varying unrolling factor.                                                                                                               | 113 |

| TABLE 5.9:  | Examples of matrix-vector multiplication with $m \times n$ matrix $A$ using loop interchange ( $c = A \times b$ ).                                                                       | 113 |

| TABLE 5.10: | The memory access pattern for the loop interchange algorithm with $4\times4$ matrix $A$ in column-major order layout scheme shown in Table 5.9 (b).                                      | 114 |

| TABLE 5.11: | The performance of loop interchange algorithm with varying problem size $n$ .                                                                                                            | 115 |

| TABLE 5.12: | The example of matrix-vector multiplication with $m \times n$ matrix $A$ using vectorization ( $c = A \times b$ ).                                                                       | 117 |

| TABLE 5.13: | The performance of vectorization algorithms with a varying problem size n and a fixed $m=1024$ .                                                                                         | 119 |

| TABLE 5.14: | The conventional serial algorithm for multiplying of two $n \times n$ square matrices.                                                                                                   | 121 |

|             |                                                                                                                                                                                                                                                                                                                                             | xiv |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TABLE 5.15: | The summary of our implementation techniques of matrix multiplication used for our platforms.                                                                                                                                                                                                                                               | 126 |

| TABLE 5.16: | The performance (GFLOPS) for varying schedules and sizes of L1-block ( $b_1$ ) with fixed size of L2-block ( $b_2$ =512) and register-block ( $b_0$ =4) on a single core of Intel Clovertown platform. We use 1DF scheduling scheme for L1-level and L2-level blocking, and vary the scheduling scheme at the register level.               | 130 |

| TABLE 5.17: | Cache miss rate $(\%)$ and system bus bandwidth utilization $(\%)$ on Intel Clovertown platform.                                                                                                                                                                                                                                            | 132 |

| TABLE 5.18: | The performance (GFLOPS) for different multi-buffering schemes and size of LS-block $(b_1)$ with fixed size of the register-block $(b_0=4)$ on a single SPE of IBM Cell/B.E. platform. We use the 1DF scheduling scheme for both level blocking.                                                                                            | 134 |

| TABLE 5.19: | The naïve serial 3D-FDTD algorithm.                                                                                                                                                                                                                                                                                                         | 138 |

| TABLE 5.20: | The summary of our implementation techniques of 3D FDTD for our platforms.                                                                                                                                                                                                                                                                  | 140 |

| TABLE 5.21: | The pseudo code for the SPE 3D-FDTD <b>E</b> -field computation using double buffers.                                                                                                                                                                                                                                                       | 143 |

| TABLE 5.22: | The performance (GFLOPS) for different register level schedules and sizes of L1-block $(b_1)$ with fixed size of L2-block $(b_2=64)$ and register-block $(b_0=4)$ on a single core of the Intel Clovertown platform. We use 1DF scheduling scheme for L1-level and L2-level blocking, and vary the scheduling scheme at the register level. | 144 |

| TABLE 5.23: | Cache miss rate (%) and system bus bandwidth utilization (%) on Intel Clovertown platform.                                                                                                                                                                                                                                                  | 145 |

| TABLE 5.24: | The LU decomposition based on Gaussian elimination method with $n \times n$ square matrix $A$ .                                                                                                                                                                                                                                             | 149 |

| TABLE 5.25: | The summary of our implementation techniques of LU Decomposition for our platforms.                                                                                                                                                                                                                                                         | 151 |

| TABLE 5.26: | The different tasks of the four blocks at <i>d</i> -level.                                                                                                                                                                                                                                                                                  | 153 |

| TABLE 5.27: | Pseudo-code of naïve serial algorithm for the bus and branch computations.                                                                                                                                                                                                                                                                  | 160 |

| TABLE 5.28: | The summary of our implementation techniques of PFS-GS for our platforms.                                                                                                                                                                                                                                                                   | 163 |

|             |                                                                                                                                                                                          | XV  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TABLE 5.29: | Pseudo code of the multicore-efficient implementation for PFS- GS on the IBM Cell/B.E. platform.                                                                                         | 166 |

| TABLE 5.30: | GFLOPS with varying DMA transfer size in bytes on single SPE.                                                                                                                            | 168 |

| TABLE 5.31: | Distributed speedup and % of computation on single SPE; Note our multicore-efficient implementation combines both double-buffering scheme and vectorized unified-bus-computation module. | 169 |

#### **CHAPTER 1: INTRODUCTION**

## 1.1 Rise of Multicore Computing

Since the introduction of the microprocessor in the mid-70s the computer industry has pursued a uniprocessor hardware architecture paradigm accompanied by a sequential programming model. The steady growth in performance over the years was achieved primarily through a steady increase of clock frequency enabled by scaling of the underlying transistors. Architectural innovations such as hardware controlled on-chip memory hierarchies (caches) were introduced so that the increasing gap between the processor speeds and the memory access latencies could be hidden from the programmer. At the chip level, application parallelism was primarily exploited at the instruction level in a manner transparent to the programmer through multiple execution pipelines and out-of-order processing controlled by complex logic.

However, by the middle of this decade, the traditional uniprocessor architecture performance had hit a roadblock due to a combination of factors, such as excessive power dissipation due to high operating frequencies, growing memory access latencies, diminishing returns on deeper instruction pipelines, and a saturation of available instruction level parallelism in applications. An attractive and viable alternative to improve performance are multicore processors where multiple processor cores, interconnects, and both shared and private caches are integrated on a single chip. The individual cores are often simpler than uniprocessor counterparts, exploit instruction level

parallelism adequately, and typically achieve better performance-power figures. Moreover, multicore architectures allow the programmer to exploit multiple levels of parallelism at the data and task level than was possible with a traditional uniprocessor. From a modest beginning of dual and quad cores, multicore processors are expected to include hundreds of cores in a single chip in the near future. Currently almost all of the high performance processors offered by leading industry vendors such as Intel, IBM, AMD and Sun subscribe to the multicore paradigm.

#### 1.2 Research Goals

As discussed in the previous section, programmers can no longer expect continued increases in software performance without developing parallel, memory hierarchy friendly software that can effectively exploit the chip level multiprocessing paradigm of multicores. Further, due to power issues favoring architectures with lower clock frequencies and simpler in-order processing cores, the single threaded performance of commercial multicores may actually suffer in the coming years. Unfortunately, there is no easy solution to this problem. In many cases, serial code cannot be parallelized without investing considerable time and effort. Also, existing parallel libraries are often not designed to exploit the on-chip shared memory hierarchy characteristic of multicore processors. Piecemeal solutions developed for specific architectures run the risk of being non-portable not only across different architectures, but also across future versions of the same architecture. Considerable effort continues to be made in developing tools that seek to generate parallel code starting from a serial code base with minimal effort. Although this approach has its merits in terms of short term productivity, we argue in this dissertation that over the long term, a systematic design process that starts from the

sequential algorithm of the problem and develops a scalable, parallel, memory hierarchy friendly algorithm with tunable parameters has the best chance of avoiding technology obsolescence. Note that the choice of an appropriate machine model is an important element of this approach. The goal of this dissertation is to demonstrate a design process for data parallel problems that starts with a sequential algorithm and ends with a high performance implementation on a multicore platform. The dissertation focuses on data parallel algorithms since they are the basis of several scientific computing kernels where high performance is critical.

While elements of the proposed design process have been reported previously, the focus has tended to be either on theoretical algorithm analysis or on code engineering, limiting its utility to programmers. The focus of our work is to provide the programmer with a design process that integrates algorithm development with actual implementation on commercial multicores. We identify and integrate recently reported research results into this design process and innovate where necessary. The flowchart shown in Figure 1.1 summarizes the multicore-efficient software design process proposed in this dissertation.

FIGURE 1.1: Design flow for multicore-efficient software design.

The inputs to the design process shown in Figure 1.1 are the target multicore platform, the parallel programming tools available for the multicore platform, and the sequential workload for the problem. The design process consists of four major steps -

We first profile the sequential workload on the target architecture to determine the set of candidate compute tasks whose multicore efficient implementation would improve the overall performance of the workload. This step uses available statistical profilers such as GNU's gprof, Oprofile, Intel Vtune Performance Analyzer, and Sun CoolTool. Note that in this dissertation we do not explicitly demonstrate this step but assume that the candidate compute kernels are known.

The second step theoretically analyzes the candidate tasks with the goals of identifying data and task parallelism, improving data locality for cache-efficient and space-efficient implementation, and identifying opportunities for overlapping computing and data transfer. The theoretical analysis is based on an appropriate machine model for the target multicore platform. The primary outputs of this step are parallel schedules for computation at different levels of the memory hierarchy, theoretical bounds on execution time under these schedules, and candidate tuning parameters.

The third step focuses on developing multicore-efficient software implementations of the candidate tasks by integrating the results of the theoretical analysis with processor specific performance optimization techniques utilizing appropriate parallel programming tools. While this step is platform and programming environment specific, many of the optimization techniques are portable across different multicore platforms.

The fourth step involves verification and tuning of the performance of multicoreefficient implementation using available performance analysis tools, such as Intel

Performance Analyzer, Intel ThreadChecker, Intel ThreadProfiler, Sun Microsystems

CoolTool, Sun Microsystems Thread Analyzer and IBM Cell B.E. SDK (see Chapter 2

and 5 for more details). These tools help in monitoring parallel performance including

parallel overhead, synchronization and load-balance. The programmers can attempt to

optimize the run-time performance by varying the tuning parameters.

The steps outline above may have to be repeated iteratively until the desired performance is achieved.

#### 1.3 Dissertation Contributions

The goal of our research is to help programmers analyze and improve the performance of data parallel applications on multicore architectures. The major contributions of this dissertation are:

- (1) We present a novel weighted-vertex pebble strategy for determining efficient block size to improve data locality on multicores. The weighted-vertex pebble strategy is an extended pebble game for devising space-efficient and cache-efficient algorithm through maximal data sharing between concurrent tasks under a given scheduling strategy.

- (2) We describe an innovative data prefetching and caching strategy to determine the optimal multi-buffering scheme for compute bound and data transfer bound algorithms. The integrated data prefetching and caching strategy improves the performance by overlapping between computations and data transfers while simultaneously effectively exploiting data locality.

- (3) We illustrate a muliticore efficient design process that blends theoretical results with practical performance optimization techniques on commercial multicores. Specifically, we integrate our theoretical results with a series of in-core optimizations to develop a robust set of design techniques that scale well both with the problem size and the number of cores on a variety of multicore architectures.

- (4) We develop multicore efficient high performance computing kernels for several important scientific computing algorithms such as matrix multiplication, finite difference time domain, LU decomposition and power flow solver based on Gauss-Seidel method. These highly optimized, multithreaded libraries could be used in science and engineering applications that require maximum performance.

#### 1.4 Dissertation Outline

This dissertation describes effective data parallel computing on multicore platforms motivated by our experiences working with commercial multicore platforms. The dissertation begins with an overview of trends multicore computing in Chapter 2. We focus on the important developments in multicore architecture, programming tools and system software.

Chapter 3 presents a design methodology that aids in the development of parallel cache-efficient and space-efficient algorithms for shared cache multicore processors. The methodology uses a weighted vertex pebbling game for maximal data sharing between concurrent tasks under a given scheduling strategy at each level of the memory hierarchy.

Chapter 4 presents algorithm specific integrated software caching and prefetching strategies. We introduce a general purpose machine model and present conditions for when the total execution time is compute bound or data transfer bound. Through case studies we illustrate the choice of optimal buffering strategy when both pre-fetching and caching is considered.

Chapter 5 describes the multicore-efficient implementations of data parallel algorithms on commercial multicore platforms. In this chapter we highlight the synthesis of the theoretical results of Chapters 3 and 4 with practical in-core optimization techniques to derive scalable multicore efficient implementations of some of the widely used scientific computing kernels. Extensive measurement results are presented on the Intel Clovertown and IBM Cell/B.E. platforms.

Chapter 6 concludes the dissertation and provides directions for future work on programming of emerging multicore architectures.

#### CHAPTER 2: TRENDS IN MULTICORE COMPUTING

### 2.1 Introduction

The rise of chip multiprocessing or the integration of multiple general purpose processing cores on a single chip (multicores), has impacted all computing platforms including high performance, servers, desktops, mobile, and embedded processors. As discussed in Chapter 1, the introduction of parallel computing at the chip level was motivated by the need to deliver Moore's law type advances in computing performance within an acceptable power budget. With this paradigm shift in computing still its early years, open questions remain on architecturally the best way to achieve this objective. Moreover, a large part of the performance of multicores hinges on the performance of parallel software that runs on them. Unfortunately, despite the progress made in developing parallel algorithms and software in the past two decades, the considerable challenges remain in its widespread adoption to the entire software stack.

Traditionally, parallel computing was largely confined to scientific computing where either custom made supercomputers or clusters of general purpose computers were employed. The parallel code necessary for these platforms were developed by application domain specialists. The rise of internet led to the development of data centers with clusters consisting of thousands of computing nodes and terabytes of storage. In the past few years, the rising costs in maintaining these data centers as well as the availability of broadband connections, has led to the emergence of "cloud computing" where both

computing resources and software are available on the "cloud" as a service [81]. However, the parallel code running on these platforms is largely web based applications characterized by embarrassing amounts of parallelism.

We note that the successful adoption of multicore processors for general purpose, scientific, and embedded computing will depend on jointly developing both the processor architecture and the software stack necessary for code developers to efficiently exploit the many types of parallelism that may exist in a computing problem. In this chapter, we review the state-of-the-art in multicore architectures (Section 2.2), parallel programming languages and tools (Section 2.3), and system software (Section 2.4). We pay special attention to the underlying trends that portend developments in each of these areas in the next few years.

#### 2.2 Multicore Architectures

In this section we examine the architectures of popular commercial multicore processors. While a plethora of such architectures exists in the embedded domain, we limit ourselves to high performance multicores where power dissipation is an important but not a dominating design issue.

#### 2.2.1 Historical Trends

The architectures of today's multicore processors are based on the uniprocessor and the shared addressed space and message passing parallel architecture designs from the past two decades. Uniprocessors have evolved from a simple RISC based pipeline of the eighties to the superscalar, RISC-CISC architectures with deep execution pipelines and out-of-order execution. Also, the increasing gap between processor and the external memory latencies requires the use of deep on-chip cache hierarchies for good memory

performance. The architectural goal of these processors was to exploit as much single thread performance as possible through aggressive exploitation of Instruction Level Parallelism (ILP). Considerable logic and power budget was devoted to dynamically finding and scheduling instructions to maximally utilize the pipelines. However, the diminishing returns on the power-performance of this approach limited the continued pursuit of performance solely through ILP.

Parallel machines evolved from the Cray vector machines implementing the Single Instruction Multiple Data (SIMD) paradigm to commodity processors connected by Commercial-Off-The-Shelf (COTS) network implementing the Single Program Multiple Data (SPMD) paradigm. Parallel machine organization can be classified into two main types – a) Shared Memory Processors (SMP) where all the processors share a common memory address space and b) Message Passing Processors (MPP) where the memory address space is disjoint and explicit messages are sent between the processors. Commercial SMPs typically employ a bus based interconnect and provide hardware cache coherence. Bus contention and the difficulties in scaling the cache coherence protocols limit the number of processors to around 32. MPPs employ point-to-point COTS network such as Ethernet (Beowulf cluster) or specialized network (IBM Blue Gene/L). The disjoint address space, lack of hardware memory coherence, and the use of scalable interconnect allows for MPPs with hundreds of processors. A great majority of the TOP500 supercomputers are MPPs.

As will be seen in the next couple of sub-sections chip level multiprocessing has borrowed a number of ideas from the above described sequential and parallel computer architectures.

#### 2.2.2 Architectural Elements

Architecturally multicore processors can be classified on the basis of a) the processing elements, b) the memory system, and c) interconnect.

## **Processing Elements:**

High performance multicore processors today adopt a mix of two design extremes - for a given transistor budget integrate a small number of complex superscalar, superpipelined cores with out-of-order processing (example Intel Xeon Clovertown quadcore), or a large number of simple in-order cores (example Sun UltraSPARC T1). The complex cores are geared towards applications requiring good single thread performance while the large number of simple cores target applications with abundant thread level parallelism. Interestingly in multicores with simple cores, the operating frequency is far below the maximum allowed by the process technology so as to manage the power budget. In either case, Symmetric Multi-Threaded (SMT) cores are utilized to manage the memory latency. While most high performance multicores have homogenous cores, processors with heterogeneous cores specialized for different application domains have also made their appearance. The Instruction Set Architecture (ISA) of the cores is an extension of the ISA of the corresponding unicores (example x86, SPARC, Power) with additional instructions such as atomic operations to support synchronization. The use of legacy ISAs allows the execution of the existing software without recompilation.

### Memory System:

Most of the high performance multicore processors in the market today follow the shared address space architecture described in Section 2.2.1. However, shared memory multicore processors differ from traditional SMPs in the following three significant ways-

- (1) The processing cores, the interconnect, and a part of the shared memory hierarchy are on the same chip/module resulting in potentially lower communication and synchronization costs.

- (2) The shared memory (typically the L2 or L3 cache) is not only shared by all or a subset of the processing cores but is of a limited size.

- (3) The integration of the processing cores, the interconnect, and the cache hierarchy on a single chip necessitates micro-architectural tradeoffs between the performance, die area, and power budgeted to the different components.

Hardware support for cache coherence is typically provided following either the broadcast (ordered interconnect) or directory based protocols (ordered and unordered interconnects). In principle the concept of a shared addressed space makes programming simple. However, in practice, since shared memory does not provide implicit synchronization of parallel tasks, memory consistency models and synchronizations routines are needed to provide the necessary synchronization. The complex interaction of synchronization, coherence, and consistency has the potential to complicate the programming and also limit the core scaling in these processors. An example of a commercial processor using the shared memory paradigm is the Intel Xeon Clovertown quad-core processor (see Section 2.2.3).

Message passing multicores have also made their appearance commercially. Here the processing cores are cache-less but instead has software managed local memory. Messages are passed between the cores on high speed on chip interconnect through Direct Memory Access (DMA) type operation. The sending and receiving of the messages implicitly synchronizes the processors. While a better hardware

power/performance is possible with this approach, the machines are harder to program. An example of a commercial processor using the shared memory paradigm is the IBM Cell Broadband Engine Processor (See Section 2.2.3).

Taking advantage of the ample on-chip bandwidth in multicores, a new protocol known as Transactional memory Coherence and Consistency (TCC) has been introduced. TCC is an extension of the shared address space paradigm, where, instead of load/store operations, atomic transactions are the basic unit of parallel work, communication, coherence, and consistency [36]. As described by Hammond et. al. "TCC hardware combines all writes from each transaction region in a program into a single packet and broadcasts this packet to the permanent shared memory state atomically as a large block. This simplifies the coherence hardware because it reduces the need for small, low-latency messages and completely eliminates the need for conventional broadcast cache coherence protocols, as multiple speculatively written versions of a cache line may safely coexist within the system. Meanwhile, automatic, hardware-controlled rollback of speculative transactions resolves any correctness violations that may occur when several processors attempt to read and write the same data simultaneously. The cost of this simplified scheme is higher interprocessor bandwidth". A commercial processor incorporating TCC is the Sun Microsystems' Rock multicore (see Section 2.2.3).

#### *Interconnect:*

The on-chip interconnect found in today's commercial high performance multicores include point-to-point, ring, bus, and crossbar. Bus has the simplest design and has global ordering that supports broadcast cache coherence protocols. However, buses do not scale well. Crossbar is unordered and offers low latency but does not scale well

either. Point-to-point interconnect (such as Intel QPI and AMD Hyper transport) has good performance but scales poorly.

## 2.2.3 Case Studies

In this section, we briefly describe the architectural features of the state-of-the-art high performance multicores available in the market today. The multicore processors presented illustrate the different design elements described in the previous sections.

### 2.2.3.1 Intel Gainestown

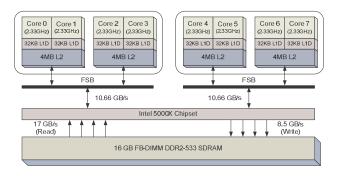

Intel Gainestown (Xeon W5500 series) was released in November 2008 by Intel based on the Nehalem microarchitecture and is currently manufactured in a 45 nm process. Nehalem is based on a multicore design philosophy of integrating a modest number of homogeneous complex cores with good single thread performance. Figure 2.1 shows the organization of the Nehalem processors.

FIGURE 2.1: Organization of the Nehalem processors.

#### Processor Cores:

Gainestown is a true quad core processor with an operation frequency of up to 3.2 GHz consuming about 130W. The x86 based cores are out-of-order and is Simultaneously Multi Threaded (SMT) supporting two threads per core. Each core can issue 4-double precision floating point operations per clock. The cores incorporate Intel's Turbo Boost Technology which allows active processor cores to run faster when there is available headroom with power, temperature, and temperature specification limits. Gainestown also incorporates Application Targeted Accelerators (ATA) which are low latency, low power, and fixed function accelerators on the processor die targeted at specific applications. The seven ATAs target string and text processing operations. Integrated power gates allow the individual idling cores to be reduced to near-zero power independent of other cores, reducing the idle power consumption to 10 W.

# Memory System:

Gainestown has a three level on-chip cache hierarchy with private 64 KB L1 cache (32 KB data + 32 KB instruction), 256 KB L2 cache, and an 8 MB L3 cache shared by all cores [82]. A 512 entry second level TLB is included to improve performance. The Nehalem implements a cache coherent Non Uniform Memory Architecture (ccNUMA) with a broadcast based MESIF cache coherence protocol [53]. The MESIF protocol extends the MESI protocol with a "Forwarding" state that allows unmodified data shared by two processors to be forwarded to a third processor. Programmers must consider the NUMA nature of the architecture in accessing data from a remote socket compared to a local DRAM.

#### Interconnect:

The Nehalem micro-architecture uses a point-to-point interconnect that uses the Intel QuickPath Technology. The interconnect uses up to 6.4 Giga transfers/second links, delivering up to 25 GB/s of total read bandwidth per core. Each processor integrates a triple channel integrated memory controller with a peak bandwidth of 32 GB/s with DDR3-1333 DIMMs.

#### 2.2.3.2 Sun UltraSPARC T2

The Sun UltraSPARC T2 was released in 2007 by Sun Microsystems based on the UltraSPARC architecture and the SPARC ISA. The UltraSPARC T2 is currently manufactured in a 65 nm process. UltraSPARC micro-architecture is based on a multicore design philosophy of integrating a large number of homogeneous simple highly multithreaded cores targeting application task level parallelism. Figure 2.2 shows the organization of the UltraSPARC T2 processor.

FIGURE 2.2: Organization of the UltraSPARC T2 processor.

#### Processor Cores:

The UltraSPARC T2 is an 8 core processor each with full hardware support for executing 8 independent threads. The in-order cores run at an operating frequency of up to 1.4 GHz with a total power consumption of about 84W. Each core consists of two integer execution units, a floating point and graphics unit, and a cryptographic stream processing unit [63]. UltraSPARC T2 implements a fine-grained multi-threading scheme where the threads are switched on a cycle-by-cycle basis between the available threads within the two statically partitioned thread groups of 4 threads each. When a thread encounters a cache-miss it is made unavailable and the instructions from it are not issued. In each cycle two instructions can be issued from each thread group. UltraSPARC T2 seeks to minimize power consumption through limited execution speculation, control and data-path clock gating, and through external power throttling.

# Memory System:

The UltraSPARC T2 has a two level on-chip cache hierarchy with a private L1 cache and a shared L2 cache. The 4 MB L2 cache is 16-way set associative with a line size of 64 bytes and organized as 8 banks. The L1 data cache is 8 KB and the instruction cache is 16 KB. The L1 caches are write through, with allocate on loads and no-allocate on stores. The L2 cache maintains a directory of L1 tags. The directory maintains a shares list at the level of L1 line granularity. Local caches are not update by stores till the L2 is updated. However, in the meantime, the same thread can see its stores.

#### *Interconnect:*

The UltraSPARC T2 uses non-blocking pipelined crossbars interconnect that connects the 8 cores to the 8 banks and the I/O port. The crossbar has a total write

bandwidth of 90 GB/s and a read bandwidth of 180 GB/s. The L2 cache connects to a 4 on-chip memory controllers interfacing to FBDIMM channels. The peak memory bandwidth is 50 GB/s for read and 26 GB/s for writes. The crossbar establishes memory order between transactions from the same and different L2 banks.

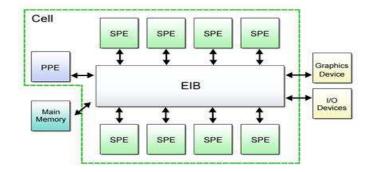

## 2.2.3.3 IBM Cell Broadband Engine

The Cell Broadband Engine introduced by IBM in 2006 is a heterogeneous multicore processor initially targeted for game consoles and consumer media applications. The processor is currently manufactured in a 45 nm technology. Figure 2.3 shows the organization of the Cell Broadband Engine.

FIGURE 2.3: Organization of the Cell Broadband Engine.

The Cell processor consists of a Power Processor Element (PPE) and 8 identical Synergistic Processor Elements (SPE). The PPE contains a 64 bit PowerPC architecture core and is primarily intended for control processing, running operating systems, managing system resources and running SPE threads. The SPE is a vector processor supporting a specialized SIMD instruction set architecture for compute intensive operations. An important difference between the SPE and the PPE is in the way memory

is accessed. The PPE uses load and store instructions to transfer instructions and data from the main memory to the register files using a two level cache hierarchy. The SPE uses Direct Memory Access (DMA) to transfer data from the main memory to a private Local Store (LS) memory through the high speed Element Interconnect Bus (EIB). Note that the SPE and PPE have two distinct ISAs necessitating the use of two different compilers. A more detailed description of the different units of the Cell processor emphasizing the different levels of parallelism supported by each is given below.

### *Power Processing Element:*

The PPE is a Power ISA based dual issue, in-order execution design, 2-way Symmetric Multi-Threaded (SMT) processor with the design optimized for frequency and power efficiency [42]. The two simultaneous threads of execution give software the effective appearance of two independent processing units with shared data flow. The PPE cache hierarchy consists of a 32 KB L1 data cache, a 32 KB L1 instruction cache, and 512 KB unified L2 cache. The second-level cache and the address translation caches use replacement management tables that allow the software to direct entries with specific address ranges to a particular subset of the cache [42]. The PPE consists of the Instruction Unit (IU), the fixed point unit (XU) and the vector scalar unit (VSU). The IU fetches four instructions per cycle per thread into an instruction buffer and after decode and dependency checking dual issues these to the execution unit. All dual issue combinations are possible with the exception of instructions to the same execution unit and some exceptions as described in [42]. The XU has 32 64-bit general purpose register file per thread, a fixed point execution unit and a load store unit. The L1 D-cache associated with the XU is non-blocking allowing cache hits under misses. The VSU issue queue

decouples vector and floating point pipelines from the other pipelines allowing vector and floating point instructions to be issued out of order with respect to other instructions. The VSU floating point units has 32 64-bit register file per thread and a 10-stage double precision floating point unit. The VSU vector unit has 32 128-bit vector register file per thread and all instructions are 128-bit SIMD with varying lengths [42].

As can be seen from the above description of the architecture, the PPE allow exploitation of parallelism at multiple levels. The dual-issue nature of the architecture allows exploitation of ILP [35]. Further, ILP partially hides memory latency by concurrently servicing multiple outstanding cache misses [35]. Such Memory Level Parallelism (MLP) can also be used between threads to increase overall memory bandwidth utilization by enabling interleaving of multiple memory transactions. However, lack of instruction re-ordering capability and sharing of execution units limits the effective exploitation of ILP on the PPE. The architects favored these limitations of dual-issue for power efficiency [35]. The SIMD instruction set enables exploitation of Data Level Parallelism (DLP). The dual threaded nature of the PPE supports Thread Level Parallelism (TLP).

## Synergistic Processing Element:

The SPE consists of a Synergistic Processing Unit (SPU) and a Memory Flow Controller (MFC). The SPU is a RISC core with a 256 KB software-controlled LS for instruction and data, and a 128-bit 128 entry unified register file. The execution units of the SPU are 128-bit wide and all instructions are 128-bit SIMD with varying widths [42]. The SPE ISA provides a rich set of vector such as arithmetic, logical, and load/store operations that can be performed on 128-bit vectors of either fixed point or floating point

values. The ISA also provides instructions to access scalars from vector registers enabling scalar operations on the SPE. Up to two instructions are issued per cycle, with one slot support fixed/floating point instructions and the other slot supporting load/store, byte permutation operations, and branch instructions. Single precision instructions are performed in 4-way SIMD fashion and are fully pipelined, while double precision instructions are performed in 4-way SIMD fashion, and are only partially pipelined. Also, double precision operations stalls the dual issue of other instructions making the Cell processor less suited for applications with massive use of double-precision instructions. The SPU assumes sequential execution of instructions leading to serious performance degradation on branch mispredictions. The ISA provides branch hint instructions enabling software to pre-fetch instructions at the target branch address.

Similar to the PPE, the SPE allows exploitation of parallelism at multiple levels. The SIMD instructions support DLP. ILP is obtained through the dual issue execution unit of the SPE. TLP is supported through the multiple SPE cores available on the Cell processor. At 3.2 GHz each SPE provides a theoretical peak performance of 25.6 GFlops/s of single precision performance and 2.6 GFlops/s of double precision performance.

## Memory Flow Controller:

The MFC implements the communication interface between the SPE and PPE elements, and serves as a high-performance data transfer engine between the LS and Cell system memory. Data and instructions are transferred between the LS and the system memory through asynchronous coherent DMA commands. Since the address translation is governed by the PowerPC address and page tables, addresses can be passed between