### **RTN** (Register Transfer Notation)

- Provides a formal means of describing machine structure and function

- Is at the "just right" level for machine descriptions

- Does not replace hardware description languages

- Can be used to describe what a machine does (an abstract RTN) without describing how the machine does it

- Can also be used to describe a particular hardware implementation (a concrete RTN)

### RTN (cont'd.)

- At first you may find this "meta description" confusing, because it is a language that is used to describe a language

- You will find that developing a familiarity with RTN will aid greatly in your understanding of new machine design concepts

- We will describe RTN by using it to describe SRC

## Some RTN Features— Using RTN to Describe a Machine's Static Properties

#### **Static Properties**

- Specifying registers

- IR(31..0) specifies a register named "IR" having 32 bits numbered 31 to 0

- "Naming" using the := naming operator:

- op(4..0) := IR(31..27) specifies that the 5 msbs of IR be called op, with bits 4..0

- Notice that this does not create a new register, it just generates another name, or "alias," for an already existing register or part of a register

## Using RTN to Describe Dynamic Properties

#### **Dynamic Properties**

Conditional expressions:

$$(op=12) \rightarrow R[ra] \leftarrow R[rb] + R[rc]$$

: ; defines the add instruction

"if" condition "then" RTN Assignment Operator

This fragment of RTN describes the SRC add instruction. It says, "when the op field of IR = 12, then store in the register specified by the ra field, the result of adding the register specified by the rb field to the register specified by the rc field."

## Using RTN to Describe the SRC (Static) Processor State

#### **Processor state**

PC(31..0): program counter

(memory addr. of next inst.)

IR(31..0): instruction register

Run: one bit run/halt indicator

Strt: start signal

R[0..31](31..0): general purpose registers

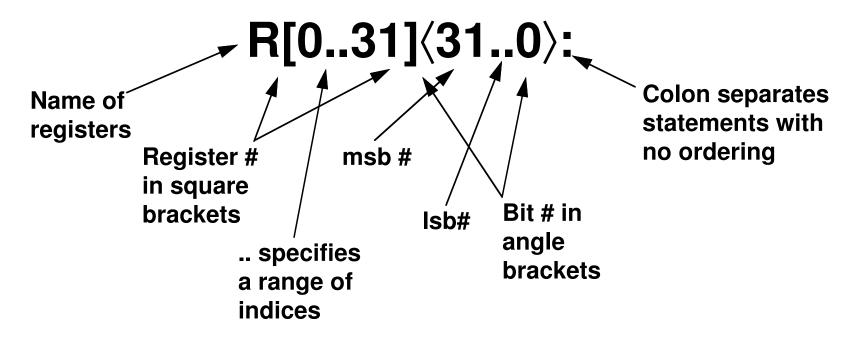

### **RTN Register Declarations**

- General register specifications shows some features of the notation

- Describes a set of 32 32-bit registers with names R[0] to R[31]

# Memory Declaration: RTN Naming Operator

- Defining names with formal parameters is a powerful formatting tool

- Used here to define word memory (big-endian)

#### Main memory state

Mem $[0..2^{32} - 1]\langle 7..0 \rangle$ : 2<sup>32</sup> addressable bytes of memory M[x] $\langle 31..0 \rangle$ := Mem[x]#Mem[x+1]#Mem[x+2]#Mem[x+3]:

Dummy Naming Concatenation operator

All bits in register if no bit index given

# RTN Instruction Formatting Uses Renaming of IR Bits

#### **Instruction formats**

$op\langle 4..0\rangle := IR\langle 31..27\rangle$ : operation code field

$ra\langle 4..0 \rangle := IR\langle 26..22 \rangle$ : target register field

$rb\langle 4..0 \rangle := IR\langle 21..17 \rangle$ : operand, address index, or

branch target register

$rc\langle 4..0 \rangle := IR\langle 16..12 \rangle$ : second operand, conditional

test, or shift count register

$c1\langle 21..0\rangle := IR\langle 21..0\rangle$ : long displacement field

c2(16..0) := IR(16..0): short displacement or

immediate field

$c3\langle11..0\rangle := IR\langle11..0\rangle$ : count or modifier field

### Specifying Dynamic Properties of SRC: RTN Gives Specifics of Address Calculation

Effective address calculations (occur at runtime):

```

disp\langle 31..0 \rangle := ((rb=0) \rightarrow c2\langle 16..0 \rangle {sign extend}: displacement (rb\neq 0) \rightarrow R[rb] + c2\langle 16..0 \rangle {sign extend, 2's comp.}): address rel\langle 31..0 \rangle := PC\langle 31..0 \rangle + c1\langle 21..0 \rangle {sign extend, 2's comp.}: relative address

```

- Renaming defines displacement and relative addresses

- New RTN notation is used

- condition → expression means <u>if</u> condition <u>then</u> expression

- modifiers in { } describe type of arithmetic or how short numbers are extended to longer ones

- arithmetic operators (+ \* / etc.) can be used in expressions

- Register R[0] cannot be added to a displacement

## Detailed Questions Answered by the RTN for Addresses

- What set of memory cells can be addressed by direct addressing (displacement with rb=0)

- If c2(16)=0 (positive displacement) absolute addresses range from 00000000H to 0000FFFFH

- If c2(16)=1 (negative displacement) absolute addresses range from FFFF0000H to FFFFFFFH

- What range of memory addresses can be specified by a relative address

- The largest positive value of C1(21..0) is 2<sup>21</sup>-1 and its most negative value is -2<sup>21</sup>, so addresses up to 2<sup>21</sup>-1 forward and 2<sup>21</sup> backward from the current PC value can be specified

- Note the difference between rb and R[rb]

# Instruction Interpretation: RTN Description of Fetch-Execute

- Need to describe actions (not just declarations)

- Some new notation

### RTN Sequence and Clocking

- In general, RTN statements separated by : take place during the same clock pulse

- Statements separated by ; take place on successive clock pulses

- This is not entirely accurate since some things written with one RTN statement can take several clocks to perform

- More precise difference between : and ;

- The order of execution of statements separated by

does not matter

- If statements are separated by ; the one on the left must be complete before the one on the right starts

## More About Instruction Interpretation RTN

- In the expression IR ← M[PC]: PC ← PC + 4; which value of PC applies to M[PC]?

- The rule in RTN is that all right hand sides of ":" separated RTs are evaluated before any LHS is changed

- In logic design, this corresponds to "master-slave" operation of flip-flops

- We see what happens when Run is true and when Run is false but Strt is true. What about the case of Run and Strt both false?

- Since no action is specified for this case, the RTN implicitly says that no action occurs in this case

### **Individual Instructions**

- instruction\_interpretation contained a forward reference to instruction\_execution

- instruction\_execution is a long list of conditional operations

- The condition is that the op code specifies a given instruction

- The operation describes what that instruction does

- Note that the operations of the instruction are done after (;) the instruction is put into IR and the PC has been advanced to the next instruction

## RTN Instruction Execution for Load and Store Instructions

```

\begin{array}{ll} \text{instruction\_execution} := (\\ & \text{Id} \ (:= op= 1) \to R[ra] \leftarrow M[\text{disp}] \colon & \text{load register} \\ & \text{Idr} \ (:= op= 2) \to R[ra] \leftarrow M[\text{rel}] \colon & \text{load register relative} \\ & \text{st} \ (:= op= 3) \to M[\text{disp}] \leftarrow R[ra] \colon & \text{store register} \\ & \text{str} \ (:= op= 4) \to M[\text{rel}] \leftarrow R[\text{ra}] \colon & \text{store register relative} \\ & \text{la} \ (:= op= 5) \to R[\text{ra}] \leftarrow \text{disp} \colon & \text{load displacement address} \\ & \text{lar} \ (:= op= 6) \to R[\text{ra}] \leftarrow \text{rel} \colon & \text{load relative address} \\ \end{array}

```

- The in-line definition (:= op=1) saves writing a separate definition Id := op=1 for the Id mnemonic

- The previous definitions of disp and rel are needed to understand all the details

### **SRC RTN—The Main Loop**

Thus ii and ie invoke each other, as coroutines.

## Use of RTN Definitions: Text Substitution Semantics

```

Id (:= op= 1) \rightarrow R[ra] \leftarrow M[disp]: disp\langle 31..0 \rangle := ((rb=0) \rightarrow c2\langle 16..0 \rangle {sign extend}: (rb\neq 0) \rightarrow R[rb] + c2\langle 16..0 \rangle {sign extend, 2's comp.} ): ld (:= op= 1) \rightarrow R[ra] \leftarrow M[ ((rb=0) \rightarrow c2\langle 16..0 \rangle {sign extend}: (rb\neq 0) \rightarrow R[rb] + c2\langle 16..0 \rangle {sign extend, 2's comp.} ): ]:

```

- An example:

- If IR = 00001 00101 00011 0000000000001011

- then Id → R[5] ← M[ R[3] + 11 ]:

## RTN Descriptions of SRC Branch Instructions

- Branch condition determined by 3 Isbs of instruction

- Link register (R[ra]) set to point to next instruction

```

\begin{array}{c} \text{cond} := (\text{ c3}\langle 2..0\rangle = 0 \rightarrow 0: & \text{never} \\ \text{c3}\langle 2..0\rangle = 1 \rightarrow 1: & \text{always} \\ \text{c3}\langle 2..0\rangle = 2 \rightarrow \text{R[rc]} = 0: & \text{if register is zero} \\ \text{c3}\langle 2..0\rangle = 3 \rightarrow \text{R[rc]} \neq 0: & \text{if register is nonzero} \\ \text{c3}\langle 2..0\rangle = 4 \rightarrow \text{R[rc]}\langle 31\rangle = 0: & \text{if positive or zero} \\ \text{c3}\langle 2..0\rangle = 5 \rightarrow \text{R[rc]}\langle 31\rangle = 1 \ ): & \text{if negative} \\ \text{br (:= op= 8)} \rightarrow (\text{cond} \rightarrow \text{PC} \leftarrow \text{R[rb]}): & \text{conditional branch} \\ \text{brI (:= op= 9)} \rightarrow (\text{R[ra]} \leftarrow \text{PC}: \\ \text{cond} \rightarrow (\text{PC} \leftarrow \text{R[rb]}) \ ): & \text{branch and link} \end{array}

```

### **RTN for Arithmetic and Logic**

```

add (:= op=12) \rightarrow R[ra] \leftarrow R[rb] + R[rc]:

addi (:= op=13) \rightarrow R[ra] \leftarrow R[rb] + c2\langle16..0\rangle {2's comp. sign

ext.}:

sub (:= op=14) \rightarrow R[ra] \leftarrow R[rb] - R[rc]:

neg (:= op=15) \rightarrow R[ra] \leftarrow -R[rc]:

and (:= op=20) \rightarrow R[ra] \leftarrow R[rb] \land R[rc]:

andi (:= op=21) \rightarrow R[ra] \leftarrow R[rb] \land c2\langle16..0\rangle {sign extend}:

or (:= op=22) \rightarrow R[ra] \leftarrow R[rb] \vee R[rc]:

ori (:= op=23) \rightarrow R[ra] \leftarrow R[rb] \vee c2\langle16..0\rangle {sign extend}:

not (:= op=24) \rightarrow R[ra] \leftarrow \negR[rc]:

Logical operators: <u>and \wedge or \vee and <u>not \neg</u></u>

```

#### **RTN for Shift Instructions**

- Count may be 5 Isbs of a register or the instruction

- Notation: @ replication, # concatenation

```

\begin{array}{c} n := ( \quad (c3\langle 4..0\rangle = 0) \to R[rc]\langle 4..0\rangle : \\ (c3\langle 4..0\rangle \neq 0) \to c3\langle 4..0\rangle ) : \\ shr \ (:= op=26) \to R[ra]\langle 31..0\rangle \leftarrow (n @ 0) \# R[rb]\langle 31..n\rangle : \\ shra \ (:= op=27) \to R[ra]\langle 31..0\rangle \leftarrow (n @ R[rb]\langle 31\rangle) \# R[rb]\langle 31..n\rangle : \\ shl \ (:= op=28) \to R[ra]\langle 31..0\rangle \leftarrow R[rb]\langle 31-n..0\rangle \# (n @ 0) : \\ shc \ (:= op=29) \to R[ra]\langle 31..0\rangle \leftarrow R[rb]\langle 31-n..0\rangle \# R[rb]\langle 31..32-n\rangle : \\ \end{array}

```

## Example of Replication and Concatenation in Shift

Arithmetic shift right by 13 concatenates 13 copies of the sign bit with the upper 19 bits of the operand

shra r1, r2, 13

R[2]= 1001 0111 1110 1010 1110 1100 0001 0110

$13@R[2]\langle 31\rangle$  #  $R[2]\langle 31...13\rangle$ R[1]= 1111 1111 1 1111 1 100 1011 1111 0101 0111

### **Assembly Language for Shift**

Form of assembly language instruction tells whether to set c3=0

shr ra, rb, rc

shr ra, rb, count

shra ra, rb, rc

shra ra, rb, count

shl ra, rb, rc

shl ra, rb, count

shc ra, rb, count

shc ra, rb, count

;Shift rb right into ra by 5 lsbs of rc ;Shift rb right into ra by 5 lsbs of inst ;AShift rb right into ra by 5 lsbs of rc ;AShift rb right into ra by 5 lsbs of inst ;Shift rb left into ra by 5 lsbs of inst ;Shift rb circ. into ra by 5 lsbs of rc ;Shift rb circ. into ra by 5 lsbs of inst

# **End of RTN Definition of instruction\_execution**

```

nop (:= op= 0) \rightarrow : No operation stop (:= op= 31) \rightarrow Run \leftarrow 0: Stop instruction end of instruction_execution instruction_interpretation.

```

- We will find special use for nop in pipelining

- The machine waits for Strt after executing stop

- The long conditional statement defining instruction\_execution ends with a direction to go repeat instruction\_interpretation, which will fetch and execute the next instruction (if Run still =1)

#### **Confused about RTN and SRC?**

- SRC is a Machine Language

- It can be interpreted by either hardware or software simulator.

- RTN is a Specification Language

- Specification languages are languages that are used to specify other languages or systems—a metalanguage.

- Other examples: LEX, YACC, VHDL, Verilog

Figure 2.10 may help clear this up...

### Fig 2.10 The Relationship of RTN to SRC

SRC specification written in RTN RTN compiler Generated processor SRC program Data output SRC interpreter or simulator and data

Computer Systems Design and Architecture by V. Heuring and H. Jordan

© 1997 V. Heuring and H. Jordan

### A Note About Specification Languages

- They allow the description of what without having to specify how.

- They allow precise and unambiguous specifications, unlike natural language.

- They reduce errors:

- Errors due to misinterpretation of imprecise specifications written in natural language.

- Errors due to confusion in design and implementation—"human error."

- Now the designer must debug the specification!

- Specifications can be automatically checked and processed by tools.

- An RTN specification could be input to a simulator generator that would produce a simulator for the specified machine.

- An RTN specification could be input to a compiler generator that would generate a compiler for the language, whose output could be run on the simulator.

# Addressing Modes Described in RTN (Not SRC)

|                      |                  |                                               | 1 3.1 9 2 1 2 9 2 2 2 2 |

|----------------------|------------------|-----------------------------------------------|-------------------------|

| Mode name            | <u>Assembler</u> | RTN meaning                                   | <u>Use</u>              |

|                      | <u>Syntax</u>    | <b>V</b>                                      |                         |

| Register             | Ra               | $R[t] \leftarrow R[a]$                        | Tmp. Var.               |

| Register indirect    | (Ra)             | $R[t] \leftarrow M[R[a]]$                     | Pointer                 |

| Immediate            | #X               | $R[t] \leftarrow X$                           | Constant                |

| Direct, absolute     | X                | $R[t] \leftarrow M[X]$                        | Global Var.             |

| Indirect             | (X)              | $R[t] \leftarrow M[M[X]]$                     | Pointer Var.            |

| Indexed, based,      | X(Ra)            | $R[t] \leftarrow M[X + R[a]]$                 | Arrays, structs         |

| or displacement      | , ,              |                                               | • •                     |

| Relative             | X(PC)            | $R[t] \leftarrow M[X + PC]$                   | Vals stored w pgm       |

| <b>Autoincrement</b> | (Ra)+            | $R[t] \leftarrow M[R[a]]; R[a] \leftarrow F$  | . •                     |

| Autodecrement        | · (Ra)           | $R[a] \leftarrow R[a] - 1; R[t] \leftarrow N$ | <del>-</del> -          |

|                      | ` '              |                                               |                         |

**Target register**